Automatizando o processo

Síntese

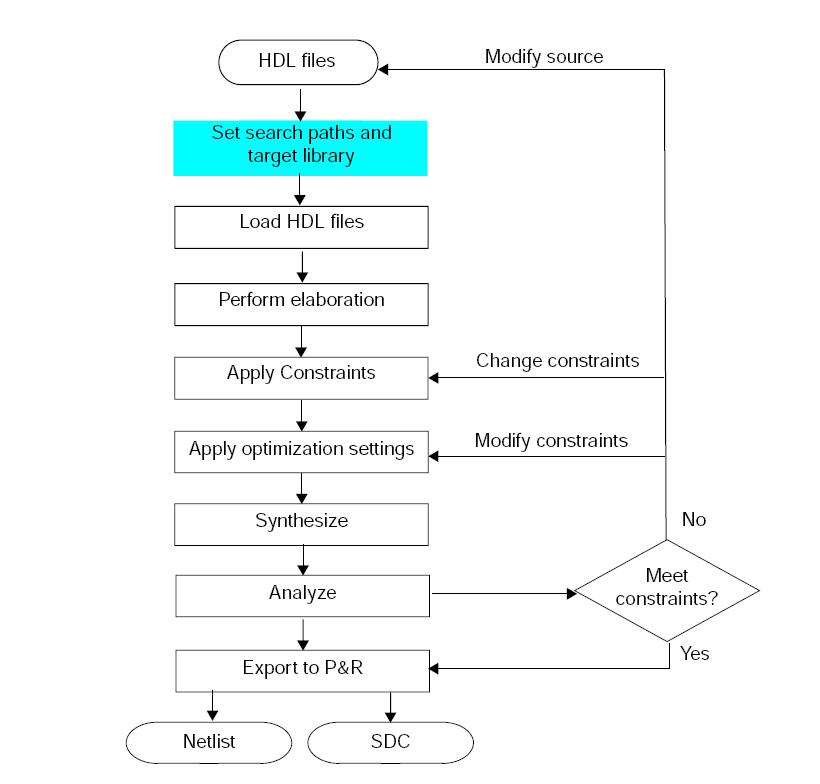

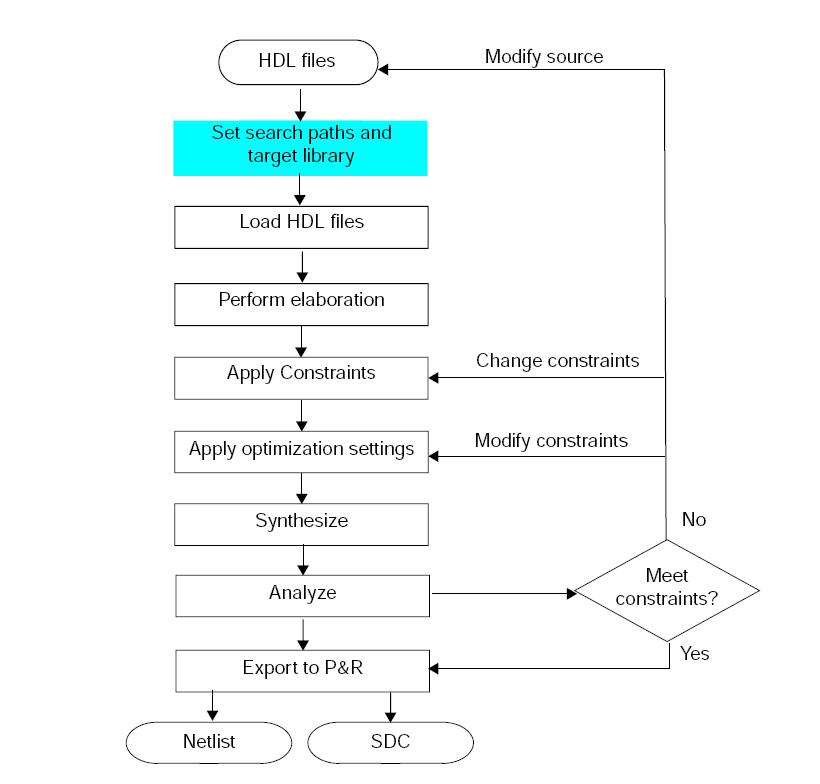

Nesta etapa foram realizadas as atividades de:

- Métodos para automatizar o fluxo;

- Definição da biblioteca;

- Carregamento dos arquivos HDL;

- Elaboração;

- Definição das restrições;

- Aplicando otimizações;

- Síntese;

- Análise;

- Modificação das restrições;

- Exportação da Netlist e das restrições para a próxima etapa;

- Simulação do resultado.

O fluxo está apresentado a seguir e está de acordo com o recomendado pela Cadence.

Automatizando

o processo

Foram criados arquivos de script para execução automática de todas as atividades de síntese. O último arquivo criado foi o auto.tcl, que gerou todos os arquivos necessários para passar à fase posterior à síntese. Detalhes sobre os comandos utilizados no arquivo auto22.tcl serão vistos adiante.

Para executar o arquivo de script entra-se no programa de síntese Cadence Encounter RTL Compiler através do comando 'rc' e após executa 'include auto22.tcl' ou, na inicialização, escreve-se 'rc -files auto22.tcl'.

Escolhendo e configurando a biblioteca

As bibliotecas disponíveis na internet, por exemplo a vtvtlib25.lib, possuem um desempenho bastante inferior ao desejado. Logo, foi utilizado a biblioteca da Cadence c35_CORELIB.lib.

Obs.: Por questões legais, não é possível disponibilizar o arquivo de biblioteca da Cadence neste tutorial.

No computador do Cin/UFPE, a biblioteca estava instalada na pasta /opt/cadence/ams_hk/ams_v3.70/liberty/c35_3.3V

Foi então setada a biblioteca através dos comandos:

set_attribute lib_search_path

/opt/cadence/ams_hk/ams_v3.70/liberty/c35_3.3V

set_attribute

library {c35_CORELIB.lib}

Lendo

os arquivos HDL

Para carregar os arquivos HDL é utilizado o comando:

read_hdl -v2001 uartproto.v uartproto_baudgen.v uartproto_transmitter.v

A opção -v2001 indica que os arquivos HDL seguem o padrão Verilog 2001

Realizando a elaboração

Nesta etapa o RTL Compiler irá:

- Construir as estruturas de dados;

- Inferir registradores no design;

- Executar otimizações no código HDL em alto nível (como retirada de código morto);

- Checar a semântica.

Para elaborar o programa deve-se digitar:

elaborate uartproto

Definição das restrições

Deve-se criar o arquivo SDC. No caso em questão, foi criado o arquivo diretivas.sdc

Neste arquivo constam algumas restrições que você pode aplicar ao compilador. Por exemplo:

A linha: create_clock -name "my_clock"

-period 10 -waveform {5 10} [get_port "csi_clockInput_clk"]

indica

que o clock será de 10ns, que do 5. ao 10. ns o clock estará

em 1, que o nome do clock será my_clock e que a porta de

entrada será a csi_clockInput_clk.

As linhas: set_input_transition -rise 0.1 [get_port

"csi_clockInput_reset_n"] e set_input_transition -fall 0.2

[get_port "csi_clockInput_reset_n"]

indicam o tempo de

subida e descida respectivamente para os sinais aplicados nas

entradas (deve-se especificar todas as entradas, inclusive o clock:

“my_clock”).

As linhas: set_load -max 10 set_load -max 1 [get_port

"sout"]

indicam a carga máxima, em fF, que estará

conectado em cada porta de saída.

Após criadas as restrições no arquivo .SDC apropriado (conforme indicado anteriormente), deve-se ler o mesmo através do comando:

read_sdc diretivas.sdc

Aplicando otimizações

As otimizações propostas no manual do RTL Encounter visam sobretudo otimizar a interconexão entre os designs criados na etapa de elaboração. Logo, como o projeto proposto neste tutorial tem apenas um design, não foi possível aplicar otimizações.

Como forma de comprovação, uma compilação padrão resultou em um slack de +5658ps e 69924 área de célula, conforme rel_sum_sint2.txt

Foi tentado agrupar e desagrupar os designs através dos comandos:

set_attribute auto_ungroup none

set_attribute

auto_ungroup timing

set_attribute auto_ungroup area

set_attribute

auto_ungroup both

Mas, como esperado, não fez diferença. Não houve nenhuma mudança nos resultados.

Foi tentado também o aplicar o autopartition, porém a especificação não é reconhecida pelo comando set_attribute. O RTL Encounter disse que era obsoleto.

Igualmente, a otimização de 'boundary' não resultou em ganhos.

Maiores detalhes sobre as otimizações, consultar o manual do RC.

Sintetizando

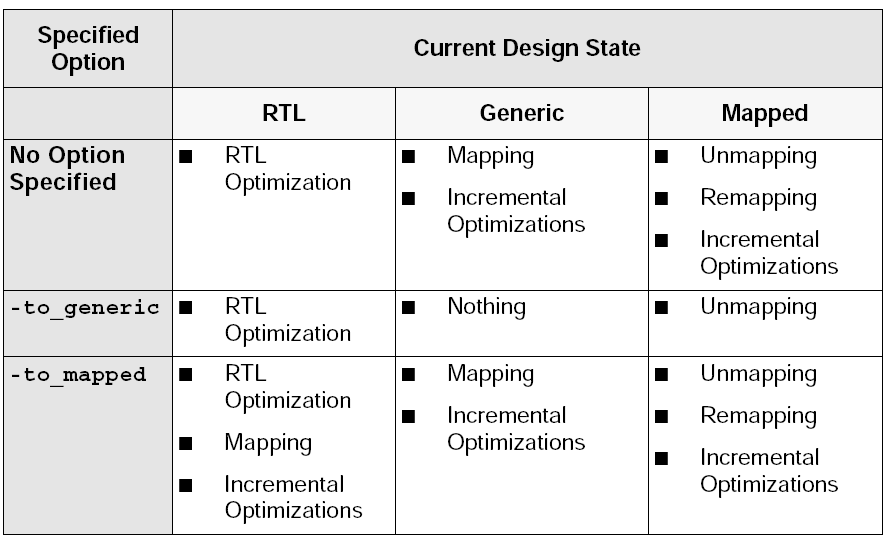

Para a síntese são utilizados basicamente dois comandos:

synthesize -to_generic

realiza uma otimização

RTL no design.

synthesize -to_mapped

realiza o mapeamento

do design RTL nas células da biblioteca de tecnologia.

Seguindo o quadro abaixo.

Obs.: Os números apresentados nesta sessão não foram obtidos com os arquivos uartproto.v, uartproto_transmitter.v e uartproto_baudgen.v fornecidos anteriormente. Porém, a partir da próxima sessão é retomado o processo de síntese com os arquivos fornecidos.

Logo, foram realizadas as seguintes tentativas:

synthesize

-to_generic -effort low

synthesize -to_mapped -effort low

slack:

+3913ps / area: 78133

conforme o rel_sum_sint14.txt

synthesize

-to_generic -effort high

synthesize -to_mapped -effort high

slack:

+2519ps / area:

68396

conforme o rel_sum_sint16.txt

synthesize

-to_generic -effort high

synthesize -to_mapped -effort

high

synthesize -to_mapped -effort high

slack:

+2389ps / area:

67795

conforme o rel_sum_sint17.txt

Ainda foram testado o 'retime'. Esta técnica é utilizada para melhorar o desempenho de circuitos seqüenciais através do reposicionamento dos registradores para reduzir o tempo dos ciclos ou reduzir a área sem modificar o tempo entre a entrada e a saída do dado. Esta técnica é utilizada geralmente nos datapath. A criação de pipelines também é possível e é outra técnica de retime.

Logo, foi testado:

retime

-prepare

retime -min_delay

slack:

+5412ps / area:

70452

conforme o rel_sum_sint19.txt

retime

-prepare

retime -min_delay

synthesize -to_mapped

-incremental

slack: +5412ps

/ area: 70088

conforme o

rel_sum_sint20.txt

retime

-prepare

retime -min_area

synthesize -to_mapped

-incremental

slack: +5412ps

/ area: 69433

conforme o

rel_sum_sint21.txt

synthesize

-to_generic -effort high

synthesize -to_mapped -effort high

retime

-prepare

retime -min_area

synthesize -to_mapped -incremental

-effort high

slack: +5744ps

/ area: 69997

conforme o

rel_sum_sint22.txt

Em

seguida foi tentado otimizar o total negative slack, através

do comando:

set_attribute endpoint_slack_opto true

Foi

tentado corrigir todos os erros DRC, através do

comando:

set_attribute drc_first true

Mas nada ocorreu nos resultados para os dois últimos comandos.

Em

seguida foi tentado tirar a otimização padrão

aplicada nos flip-flops que são 1 ou 0 constantes através

dos comandos:

set_attribute optimize_constant_0_flops false

/

set_attribute optimize_constant_1_flops false /

set_attribute optimize_constant_latches false /

Neste

caso os resultados foras:

slack: +5658ps / area: 72491

Para

a continuação do projeto foi escolhida a síntese

que resultou em menor área (mesmo com o slack inferior aos

demais – porém ainda positivo).

synthesize

-to_generic -effort high

synthesize -to_mapped -effort

high

synthesize -to_mapped -effort high

slack:

+2389ps / area:

67795

conforme o rel_sum_sint17.txt

Análise dos relatórios

Foram exportados os relatórios de tempo, área e sumário a partir dos comandos a seguir:

report

timing >> rel_tim_sint.txt

report area >>

rel_area_sint.txt

report summary >> rel_sum_sint.txt

O relatório de tempo é mostrado o caminho crítico e não foi apresentada qualquer violação, mostrando o slack de 5702ps.

O relatório de área mostrou as seguintes informações:

Instance

Cells Cell Area Net Area Wireload

---------------------------------------------------------

uartproto

274 38875 5544 10k (S)

transmitter 149 18236 2745 10k (S)

baudgen 113 18073 2061 10k (S)

Obs.: as áreas estão em nm^2.

E o relalório síntese mostrou as informações já apresentadas e também que não houve violações nas restrições de tempo de transição ou capacitâncias nas saídas.

Exportando a netlist e o arquivo de restrições para a etapa de layout

Para exportar os

arquivos para a etapa de layout deve-se utilizar os

comandos:

write_hdl > uart_sint.v

write_sdc >

diretivas_sint.sdc

Script final utilizado

set_attribute

lib_search_path

/opt/cadence/ams_hk/ams_v3.70/liberty/c35_3.3V

set_attribute

library {c35_CORELIB.lib}

read_hdl -v2001

../pre_sintese/uartproto.v

read_hdl -v2001

../pre_sintese/uartproto_baudgen.v

read_hdl -v2001

../pre_sintese/uartproto_transmitter.v

elaborate

uartproto

read_sdc diretivas.sdc

synthesize -to_generic

-effort high

synthesize -to_mapped -effort high

synthesize

-to_mapped -effort high

report timing >>

rel_tim.txt

report area >> rel_area.txt

report summary >>

rel_sum.txt

write_hdl > uart_sint.v

write_sdc >

diretivas_sint.sdc

exit

Simulando

o resultado

O comando foi o:

irun -access +rw

-gui uart.v uart_sintetizado.v gerador.v ./lib/c35_CORELIB.v

./lib/c35_UDP.v -top uart

Observar que foi necessário

incluir também os arquivos da biblioteca da Cadence uma vez

que o arquivo já está mapeado nas células da

biblioteca.

A opção -top foi incluída por que o SimVision não detectou automaticamente o top level.

O resultado da simulação pode ser visto na gráfico1 e no gráfico2.