Projeto Tese de Doutorado:

“Metodologias para Hardware Virtual

baseadas em Particionamento Temporal e Exploração de Espaço de Projeto”.

Grupo de Engenharia da Computação – CIN-UFPE

Grupo de Pesquisa em Computação Reconfigurável

Doutorando: Paulo Sérgio

Brandão do Nascimento,

Orientandor: Professor Manoel Eusébio

Alto grau de paralelismo é fundamental em

aplicações de processamento de imagem em alta velocidade. Modernos dispositivos

do tipo FPGA podem fornecer o paralelismo necessário e adicionalmente

flexibilidade. Entretanto, estes dispositivos são limitados em tamanho,

quantidade de memória disponível e pelo tempo necessário para a configuração do

hardware.

Técnicas de particionamento temporal podem ser

usadas para implementar grandes aplicações que podem ser quebradas em partições

(chamadas de contextos). Estas partições são multiplexadas no FPGA através de

técnicas de reconfiguração dinâmica.

Esta abordagem tem o efeito de aumentar a área

efetiva disponível para a implementação de sistemas, permitindo o aumento do

grau de paralelismo utilizado em cada tarefa que compõem a aplicação. O tempo de reconfiguração necessário entre

contextos pode causar degradação de

performance. Entretanto, exploração intensiva do paralelismo para o

processamento de grandes quantidades de pixeis de imagem pode compensar estes

tempos, produzindo aumento global de performance do processamento. Isto é verdadeiro para os FPGAs modernos

com velocidade de reconfiguração da lógica relativamente alta.

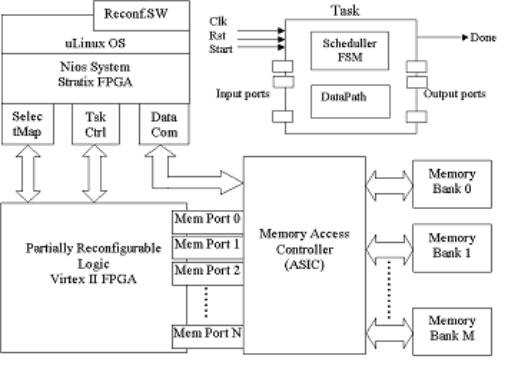

Neste trabalho de pesquisa uma plataforma de

computação reconfigurável SCR e técnicas de exploração do espaço de

projeto são propostas. Estas técnicas permitem o mapeamento de aplicações de

processamento e análise de imagens para a plataforma proposta, mostrada na

figura abaixo:

|

|

Arquitetura da plataforma para

aplicações de processamento de imagens

e interface das tarefas de hardware

Um fluxo de projeto é proposto com base no uso

de bibliotecas de implementação de componentes típicos usados em processamento

de imagem. Esta abordagem permite a separação entre as atividades de

desenvolvimento da aplicação e de projeto do hardware necessário para a

implementação física. Deste modo, o especialista em análise de imagens pode

focar seu trabalho na definição das tarefas necessárias para a aplicação e suas

relações. As implementações destas tarefas em hardware são realizadas por

especialistas de hardware que projetam os componentes necessários para serem

mapeados no FPGA.

A ortogonalidade obtida entre o projeto de

aplicação e a implementação física tem como resultado a redução do esforço de

projeto, redução na quantidade de erros durante a fase de concepção e redução

no tempo de projeto.

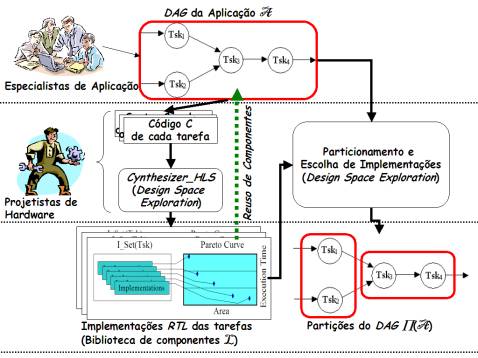

O fluxo de projeto que estamos propondo é

apresentado na figura abaixo:

|

|

Fluxo de projeto proposto

|

No fluxo proposto, um especialista da aplicação

deve especificar o sistema a ser implementado, definindo o grafo DAG com

a relação entre as tarefas e os programas em C que determinam o

comportamento de cada tarefa. A única restrição que temos considerado na nossa

proposta é que o código em C deve ser escrito utilizando o subconjunto

do ANSI C suportado pela ferramenta de síntese de alto nível (HLS)

utilizada. Isto minimizar a necessidade de refinamento manual do código

original para uma forma sintetizável e reduz o risco de modificações no comportamento

desejado devido aos refinamentos. O projetista de aplicação, deste modo,

concentra-se apenas na escolha das tarefas, dos algoritmos apropriados em alto

nível e definição das estruturas de dados da aplicação. A construção dos

componentes para implementação de cada tarefa e a exploração do espaço de

projeto fica a cargo do projetista de hardware.

O projetista de hardware tem por

atribuição realizar os refinamentos necessários na descrição em C de

cada tarefa v, exigidas pelas ferramentas de síntese de alto nível (HLS).

Em seguida, deverá gerar um conjunto de implementações possíveis L(v).

Cada implementação é descrita como código RTL sintetizável no FPGA

alvo.

Uma segunda atribuição do projetista de

hardware é definir o particionamento temporal e a escolha adequada das

implementações de tarefas, de forma que a performance desejada seja atingida.

Para isto, o projetista precisa realizar exploração do espaço de solução de

forma manual ou automática. A principal contribuição do nosso trabalho está justamente

no desenvolvimento dos métodos de exploração que permitam a obtenção de

soluções adequadas em tempo hábil.

O resultado final da atividade de

exploração do espaço de projeto consiste de uma biblioteca de componentes L, que

possuem as possíveis implementações das tarefas presentes na aplicação, e do

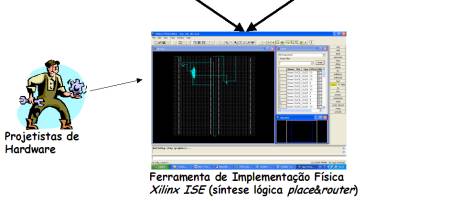

particionamento temporal P(A). O projetista de hardware deve

utilizar ferramentas de síntese lógica, placer e router para

construir a implementação física de cada partição, colocando no FPGA os

componentes escolhidos na etapa de exploração de projeto.

Reuso de componentes:

A seta pontilhada na direção ascendente

do fluxo de projeto, ver figura acima, representa a capacidade de reuso de

componentes. Em geral, cada domínio de aplicação possui um conjunto de tarefas

típicas que se repetem em diversas aplicações específicas. Por exemplo, em

aplicações de processamento de imagem, tarefas típicas são: FFT, DCT,

detecção de bordas, técnica de histograma, erosão morfológica, etc. As informações

de exploração de espaço de projeto para estes componentes (representadas por

curvas pareto ótimas de área x tempo) podem ser então armazenadas juntamente

com as implementações do componente. Na nossa proposta, estas funções

implementadas em biblioteca são disponibilizadas para reuso por parte dos

projetistas de aplicação. Desta forma, evita-se a repetição do esforço de

exploração do espaço de projeto, permitindo a diminuição do tempo de

desenvolvimento.

A biblioteca L deve disponibilizar para

o projetista de aplicação o código em C das tarefas cujas implementações

estão nela armazenadas. As informações da curva pareto ótima dos componentes

devem ser também disponibilizadas para permitir ao projetista de aplicação

realizar estimativas preliminares sobre a quantidade de recursos e sobre o

tempo de execução possível para a sua aplicação. Para o projetista de aplicação, L é vista como uma biblioteca de

funções em C que pode ser utilizada na construção de diversas aplicações.

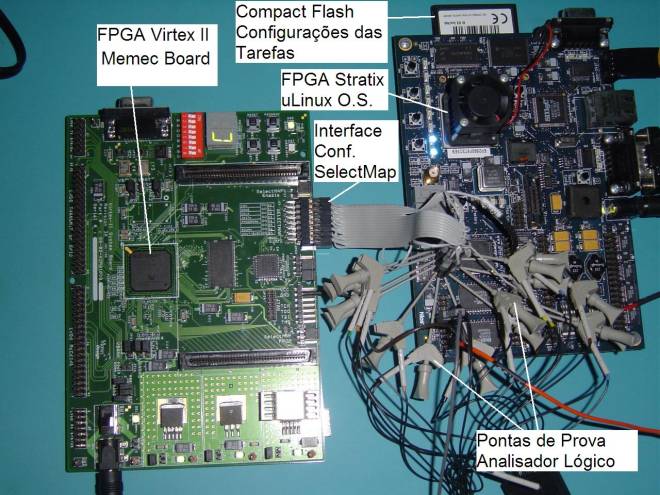

Foto do

Primeiro Protótipo do Computador Reconfigurável:

|

|

|

Protótipo Aquarius: Primeira Versão da

Plataforma |