Projeto Computador

Reconfiguravel:

Grupo de Engenharia da computação – CIN UFPE

Grupo de Pesquisa em Computação Reconfigurável

Orientador: Prof. Manoel Eusébio de Lima

Pesquisadores: Paulo Sérgio Brandão do Nascimento, Remy E.

Sant’ana, Stelita Silva, Jordana Seixas

Este projeto tem por

objetivo desenvolver um Sistema de Computação Reconfigurável para aplicações

massivas em dados, em especial aplicações de processamento de imagens.

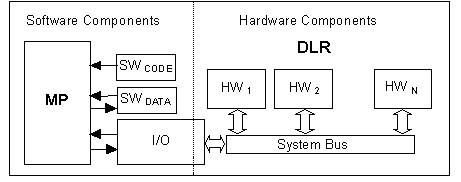

Sistemas de

Computação Reconfiguráveis (SCRs) são constituídos por componentes de

software do tipo MicroProcessador (MP) acoplados a Dispositivos de

Lógica Reconfigurável (DLR) como

é mostrado na Figura abaixo:

|

|

|

Sistema de Computação Reconfigurável |

Estes sistemas são

capazes de implementar em lógica reconfigurável (DLR) partes da

aplicação que exigem maior velocidade, permitindo maior densidade funcional

(quantidade de operações por unidade de área e por unidade de tempo) e a

exploração de paralelismo que não é possível em implementações baseadas em

software. Com isto, aumentando a performance global das aplicações.

Dispositivos de

lógica reconfigurável (DLRs) permitem a modificação dos componentes de

hardware ao longo da utilização do sistema por meio da reprogramação de sua lógica,

sem a necessidade de modificação física do hardware. Esta capacidade de

reconfiguração permite que SCRs apresentem duas importantes

características:

1. Adaptabilidade/Flexibilidade: Os componentes de hardware podem ser

implementados sobre medida para explorar características especificas de cada

aplicação. Assim, na medida que as aplicações precisam ser ativadas no SCR,

os componentes de hardware podem ser reconfigurados de forma a se adaptar as

necessidades de cada aplicação, obtendo melhor utilização dos recursos da

lógica reconfigurável e melhor desempenho.

2. Reconfiguração Dinâmica de Hardware

(RDH): Em uma aplicação

típica, nem todos componentes de hardware precisam ser ativados

simultaneamente. Desta forma, estes componentes podem ser configurados

dinamicamente (Run -Time Reconfiguration) nos DLRs, na medida que

forem necessários. Isto permite que recursos da lógica sejam compartilhados por

vários componentes de hardware, o que implica em uma grande economia destes

recursos. Aplicações que de outra forma precisariam de uma grande quantidade de

lógica para sua implementação, podem reduzir esta quantidade por meio do

compartilhamento dos recursos dos DLRs entre componentes de hardware.

Isto é possível desde que estes componentes executem suas tarefas em intervalos

de tempo diferentes (disjuntos). Esta técnica também é conhecida na literatura

com o nome de Hardware Virtual (HV) e sistemas que a utilizam são

chamados na literatura de Sistemas Dinamicamente Reconfiguráveis (SDRs)

ou Run Time Reconfigurable Systems (RTR Systems).

A construção de SCRs e SDRs

envolve a utilização de um conjunto de tecnologias de lógica

reconfigurável e metodologias de

projeto, em especial: técnicas de particionamento

hardware/software e particionamento espacial e temporal dos componentes da

aplicação. O particionamento hardware /software define quais componentes da

aplicação devem ser implementados nos dispositivos de software MP

e quais componentes devem ter sua execução acelerada através da implementação

como processos de hardware nos dispositivos reconfiguráveis DLRs. Os métodos de particionamento espacial e temporal definem o

posicionamento físico dos componentes de hardware nos DLRs bem como o comportamento temporal, estabelecendo que componentes devem

está presentes dentro da lógica em cada intervalo de tempo durante a execução.

Na Figura abaixo temos o diagrama do

sistema de computação reconfigurável que estamos desenvolvendo:

Computador

Reconfigurável em Desenvolvimento

Este sistema é composto por um

processador Nios implementado em um FPGA Stratix da Altera. Este host executa o

sistema operacional uLinux que gerencia a execução das tarefas de software e tarefas de hardware. Um FPGA Virtex II da Xilinx é utilizado para

execução das tarefas de hardware. Estas tarefas são implementadas como Cores

que são dinamicamente alocados no Virtex II,

utilizando técnicas de reconfiguração parcial e dinâmica.

O sistema utiliza um barramento padrão

AVALON com uma interface de aplicação para a comunicação entre tarefas de

hardware, software e memórias. Uma memória Compact Flash é utilizada par o

armazenamento das configurações das tarefas de hardware a serem configuradas no

Virtex II.