# Sistemas Digitais

## Operações Lógicas Mutiplexadores, demultiplexadores

Prof. Manoel Eusebio de Lima

Centro de Informática

Universidade Federal de Pernambuco

## Operações com vetores

Possíveis formas de Operação binárias

| <u> </u> | Oper. 1 | Oper. 2 | Resultado | Comentário |

|----------|---------|---------|-----------|------------|

|----------|---------|---------|-----------|------------|

- Escalar Escalar Operação padrão

- Escalar vetor Escalar N\(\tilde{a}\) o existe

- Vetor Escalar Escalar N\u00e3o existe

- Vetor Vetor Operação vetorial

- Vetor Vetor Escalar Operação relacional

- Escalar Vetor Vetor Modo Misto

- Vetor Escalar Vetor

## Aplicações lógicas com vetores

- Operações lógicas aplicadas a vetores são simplesmente uma extensão das operações lógicas como aquelas aplicadas a escalares.

- Exemplo:

$$A \neq Z := \overline{A}$$

$$A \stackrel{r}{\not\vdash}$$

$B \stackrel{r}{\not\vdash}$

$Z:=A \cdot B$

$$A \stackrel{r}{\not\vdash} Z := A + B$$

## Operações Lógicas com vetores

- Operações escalares podem ser estendidas a vetores. Estas operações são importantes no nível de sistema.

- 1. Operação lógica com vetores

- 2. Operações relacionais

- 3. Operações no modo misto

### Operações lógicas com vetores

| Operação            | Representação             | significado                      |

|---------------------|---------------------------|----------------------------------|

| NO                  | $Z:=\overline{X}$         | $z_i = \overline{x_i}$           |

| AND                 | Z:= X .Y                  | $z_i = x_i . y_i$                |

| OR                  | Z:= X +Y                  | $z_i = x_i + y_i$                |

| <b>OR-Exclusivo</b> | $Z:=X\oplus Y$            | $z_i = x_i \oplus y_i$           |

| Coincidência        | Z:= X <b>o</b> Y          | $z_i = x_i \odot y_i$            |

| NAND                | $Z:=\overline{X \cdot Y}$ | $z_i = \overline{x_i \cdot y_i}$ |

| NOR                 | $Z:=\overline{X+Y}$       | $z_i = \overline{x_i + y_i}$     |

## Operações relacionais com vetores

- Em várias tarefas de processamento é necessário verificar ou melhor comparar dois tipos de informação e tomar alguma decisão lógica. Se a decisão é verdadeira (true) ou falsa(false), em função da comparação solicitada.

- Matematicamente isto é feito através de um operador relacional. Estes operadores operam sobre vetores e produzem um resultado escalar.

Operações relacionais básicas:

< menor que > maior que

≤ menor ou igual a ≥ maior ou igual a

= igual ≠ não igual

## Aplicações - operações relacionais

- Na realização de operações relacionais deve-se tomar cuidado com o domínio dos operandos. Os operandos devem pertencer ao mesmo domínio (inteiros, ASCII, EBCDIC, ...)

- Exemplo

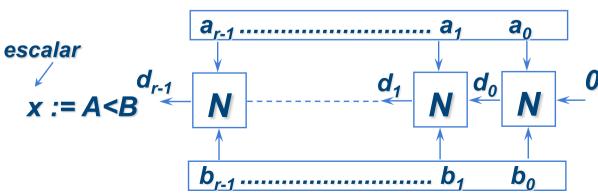

$$x := A < B$$

Para realizarmos tal operação devemos decidir qual código (domínio) será usado para representar a informação correspondente aos vetores A e B. Por exemplo A e B são números binários positivos.

Considere: A:=  $[a_{r-1}, a_{r-2}, a_0]$  e B:=  $[b_{r-1}, b_{r-2}, b_0]$

A idéia é começar a avaliar os dois vetores da direita para esquerda até encontrarmos dois bits diferentes. Se  $a_i = 0$  e  $b_i = 1$ , então sabemos que A <B e fazemos um certo  $d_i = 1$ . Este  $d_i$  funciona como um bit auxiliar para identificar a relação A < B.

## Aplicações - operações relacionais

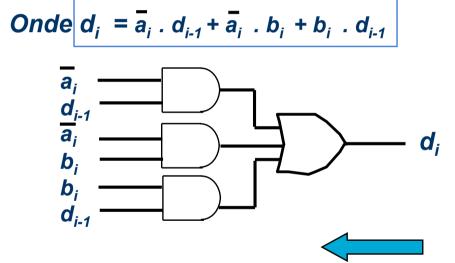

A tabela verdade para o sub-circuito que gera esta função pode ser dada por:

$$x := A < B$$

| ai | $b_i$ | d <sub>i-1</sub> | di |

|----|-------|------------------|----|

| 0  | 0     | 0                | 0  |

| 0  | 0     | 1                | 1  |

| 0  | 1     | 0                | 1  |

| 0  | 1     | 1                | 1  |

| 1  | 0     | 0                | 0  |

| 1  | 0     | 1                | 0  |

| 1  | 1     | 0                | 0  |

| 1  | 1     | 1                | 1  |

|    |       |                  |    |

## Operações no modo misto

- Existem operações onde nós desejamos combinar um escalar x com um vetor para formar um outro vetor.

- Para tal convencionamos que sendo x um escalar e Y e Z vetores, façamos:

<operação> no modo misto se

- 1. <operação> é uma das operações básicas

- 2.  $Z := x < peração > Y implica que <math>z_i := x < peração > y_i$ , para  $i = x < peração > y_i$ 1,2,...,r

- Algumas operações no modo misto

$$Z:=x.Y$$

$$z_i := x \cdot y_i$$

$i = 1, 2, .... r$

$$z_i := x \cdot y_i$$

$Z:= [0] \text{ se } x=0$

$i = 1,2, ....r$   $Y \text{ se } x=1$

$$Z := x+Y$$

$$z_i := x + y_i$$

$i = 1.2....$

$$z_i := x + y_i$$

$Z:= Y \text{ se } x=0$

$i = 1,2, ....r$   $[1,1,...] \text{ se } x=1$

## Aplicações - modo misto

### Modo Misto

Modo misto é importante quando queremos selecionar um vetor de um grupo de valores.

Suponha um circuito com três entradas W, X e Y e desejamos controlar qual vetor nós devemos usar na computação. Este é o princípio da multiplexação.

$$Z:=(a_1.W)+(a_2.X)+(a_3.Y)$$

#### Onde:

1. se

$$a_1 = 1$$

;  $a_2 = 0$ ;  $a_3 = 0$ ;  $Z := (1.W) + (0.X) + (0.Y) := W$

2. se

$$a_1 = 0$$

;  $a_2 = 1$ ;  $a_3 = 0$ ;  $Z := (0.W) + (1.X) + (0.Y) := X$

3. se

$$a_1 = 0$$

;  $a_2 = 0$ ;  $a_3 = 1$ ;  $Z := (0.W) + (0.X) + (1.Y) := Y$

Estas idéias podem ser expandidas em expressões relacionais ou expressões lógicas para computar valores de <u>a</u> nas expressões acima. Estes escalares (<u>a's</u>) são chamados variáveis de controle.

## Aplicações

Multiplexadores/Decodificadores

## Multiplexação

## Multiplexação - aplicaçãqo

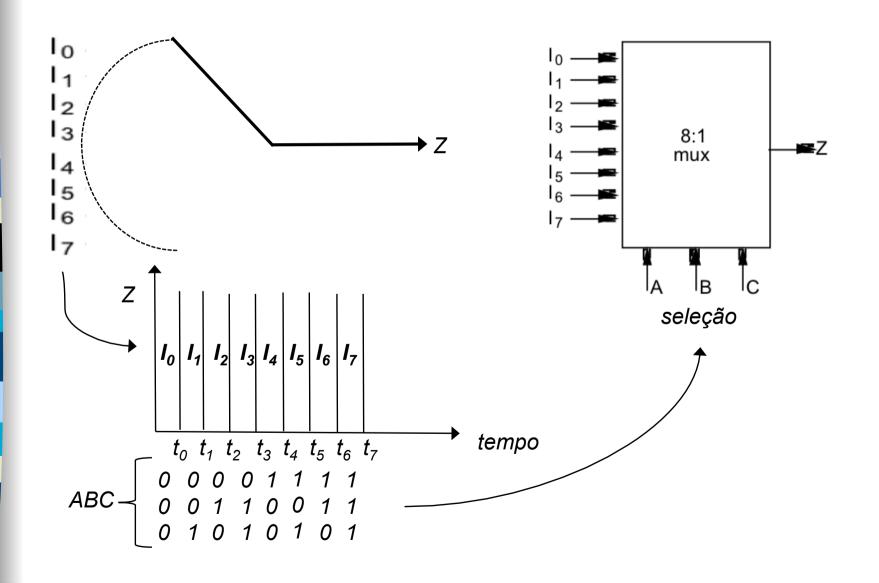

- Conceito geral

- A seleção de 2<sup>n</sup> entradas é feitas através de n linhas de controle que endereçam cada uma destas entradas para a saída.

- Cada entrada possui um endereço determinado, o qual é, em geral, associado a um minitermo.

- A saída recebe o valor da entrada correspondente ao endereço escolhido.

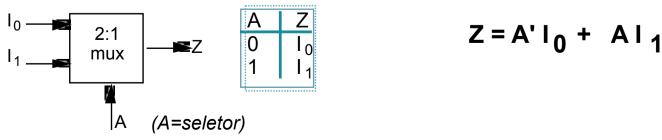

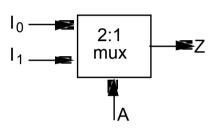

- Exemplo de um multiplexador/selector de duas entradas e uma saída (mux 2->1)

$$Z = A' I_0 + AI_1$$

A seleção em um multiplexador pode ser dado em geral por: n = número de variáveis

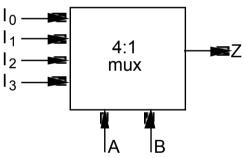

$$Z=\sum_{k=0}^{2^{n}-1} m_k I_k$$

de seleção  $m=minitermo$   $I=entrada$

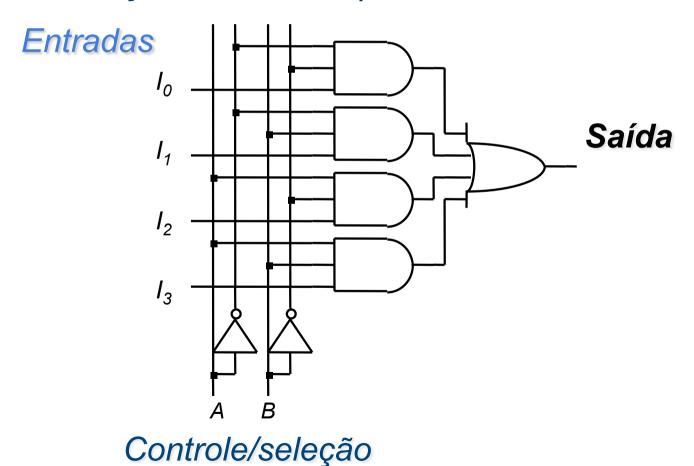

Implementação de um multiplexador 4:1

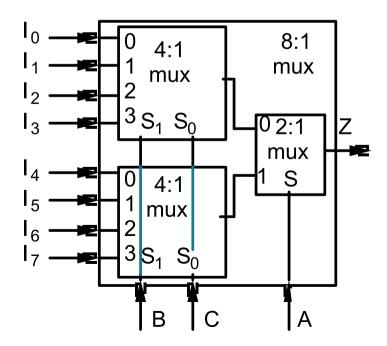

- Implementação de grandes multiplexadores a partir de pequenos multiplexadores

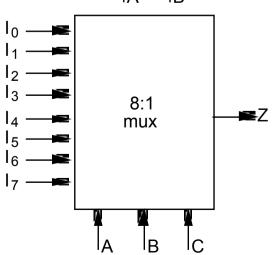

- Implementação de um multiplexador 8:1 a partir de um multiplexador 2:1 e multiplexadores 4:1

Os controles B e C escolhem uma das entradas de  $I_0$  a  $I_3$  e ao mesmo tempo de  $I_4$  a  $I_7$  entre os muxs 4:1.

O controle A estabelece a saída Z através da seleção no mux 2:1, cujas entradas são saídas dos muxs 4:1

| Α      | В        | С  | Z              |

|--------|----------|----|----------------|

| 0      | 0        | 0  | I <sub>0</sub> |

| 0<br>0 | / 0<br>0 | 1  | l <sub>1</sub> |

| 0      | 1        | 0  | l <sub>2</sub> |

| 0      | 1_       | 1  | اء             |

| 1      | 0        | 0  | I <sub>4</sub> |

| 1      | 0        | 1  | I <sub>5</sub> |

| 1      | 1        | 0  | I <sub>6</sub> |

| 1      | 1        | 1/ | l <sub>7</sub> |

■ Exemplo de multiplexador 8:1 a partir de muxs 2:1 e

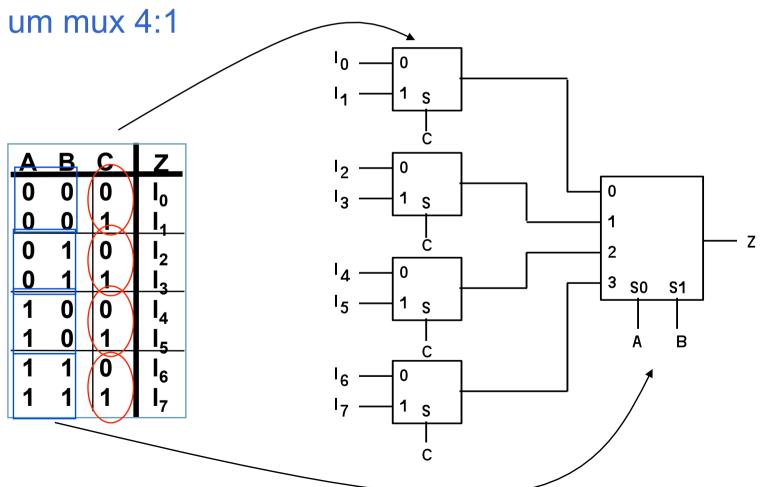

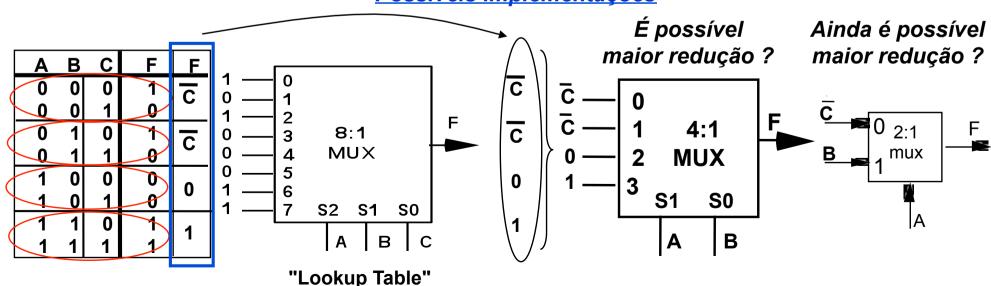

■ Multiplexadores 2<sup>n</sup>:1 podem implementar qualquer função de n variáveis, com n-1 variáveis de controle . As demais variáveis serão entrada para o mux.

#### Possíveis implementações

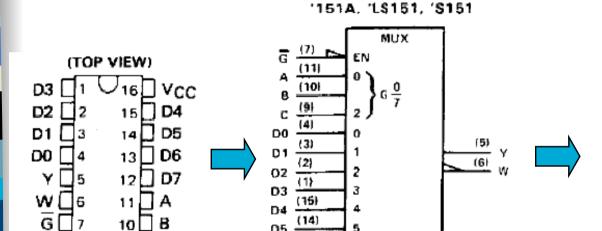

### Multiplexador comercial – 74LS151 Mux 8:1

(13)

(12)

GND □8

'151A, 'LS151, 'S151 FUNCTION TABLE

|   | II   | OUT | PUTS   |    |                 |  |

|---|------|-----|--------|----|-----------------|--|

| S | ELEC | T   | STROBE |    | W               |  |

| С | B    | A   | Ğ      |    | **              |  |

| х | ×    | х   | Н      | L  | H               |  |

| L | L    | L   | L      | DO | 00              |  |

| L | L    | Н   | L      | D1 | D1              |  |

| L | н    | Ł   | L      | D2 | $\overline{D2}$ |  |

| L | н    | H   | L      | D3 | D3              |  |

| н | Ł    | L   | L      | D4 | D4              |  |

| Н | L    | H   | L      | D5 | D5              |  |

| н | н    | L.  | L L    | Ð6 | D6              |  |

| Н | н    | н   | L      | D7 | D7              |  |

H = high level, L = tow level, X = irrelevant  $\overline{E0}$ ,  $\overline{E1}$  . . .  $\overline{E15}$  = the complement of the level of the respective E input D0, D1 . . . D7 = the level of the D respective input

## Decodificadores/Demultiplexadores

- Decodificadres/demltiplexadores são utilizados tanto para demultiplexar sinais como para decodificar endereços em um sistema computacional.

- Os decodificadores, assim como os multiplexadores também podem ser usados para implementar funções lógicas. No entanto, em geral, estes dispositivos precisam de lógica externa em sua saída.

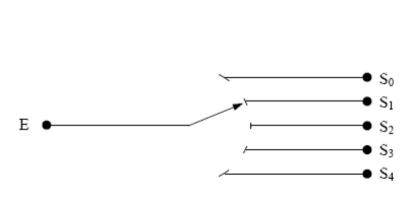

## Demultiplexador

O demultiplexador ou Demux é um circuito combinacional dedicado com a finalidade de selecionar, através das variáveis de seleção, qual de suas saídas deve receber a informação presente em sua única entrada, executando a operação inversa realizada pelo Mux.

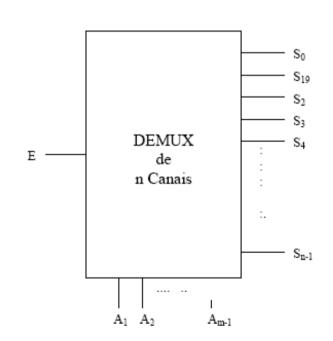

## Demultiplexador

- Da mesma forma que o Mux, no Demux o número de entradas está relacionado com o número de variáveis de seleção, ou seja:

- $n = 2^{m}$

- n número de canais de saída;

- m número de variáveis de seleção.

- Para:

- m=2 o circuito possui quatro canais de saída,

- m=3 o circuito possui oito canais de saída

- Algumas aplicações do Demux:

- seleção de circuitos que devem receber uma determinada informação digital;

- conversão de informação serial em paralela;

## Decodificadores/Demultiplexadores

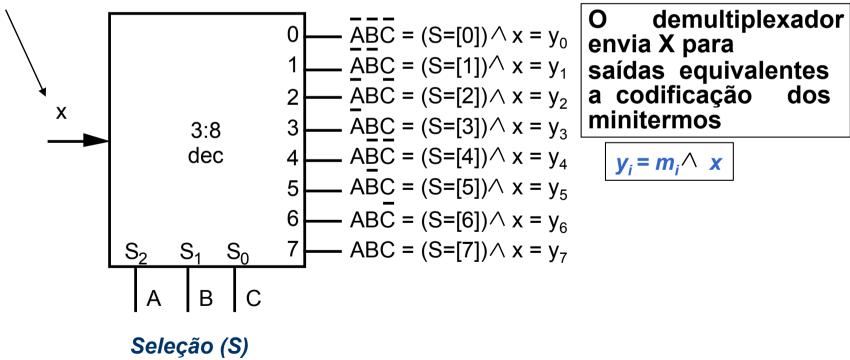

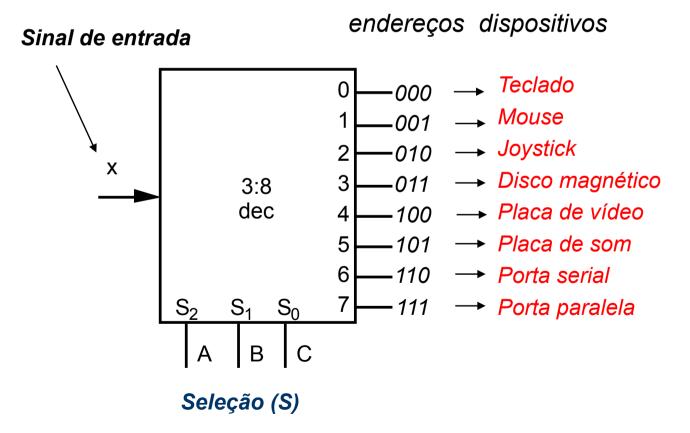

Demultiplexador/Decodificador 3:8 como bloco lógico

#### Sinal de entrada

saídas equivalentes a codificação dos minitermos

$$y_i = m_i \wedge x$$

### Decodificadores

Decodificadores de dispositivos

## Decodificadores/Demultiplexadores

Alternativas de Implementação

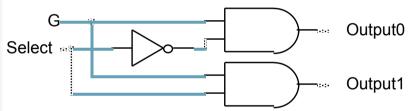

- Demultiplexador 1:2 ou

- Decodificador 1:2 com habilitação ativa em alta ("1")

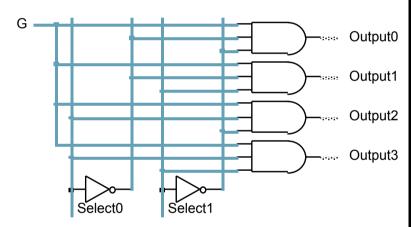

- Demultiplexador 2:4 ou

- Decodificador 2:4 com habilitação em alta ("1")

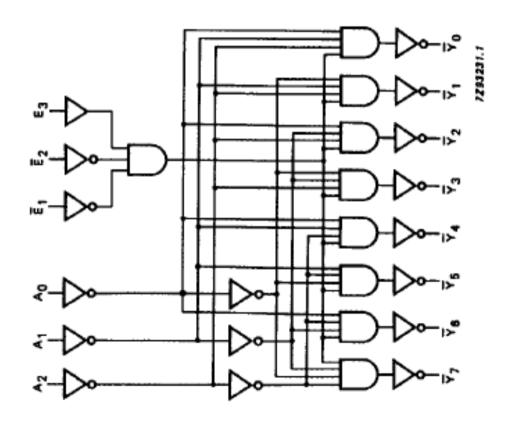

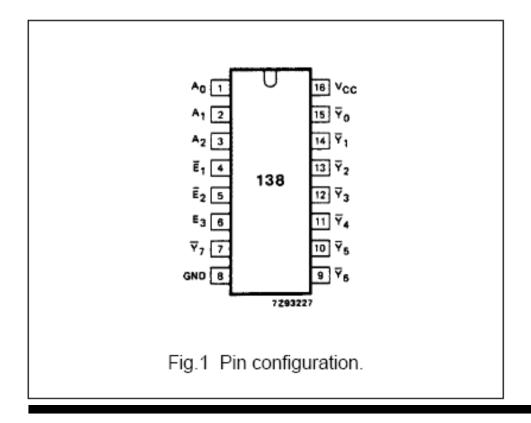

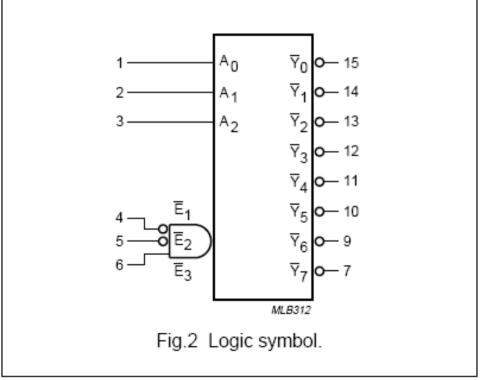

### Decodificador/demultiplexador 74138

### Diagrama Lógico

### Decodificador/demultiplexador 74138

#### PIN DESCRIPTION

| PIN NO.                      | SYMBOL                               | NAME AND FUNCTION          |

|------------------------------|--------------------------------------|----------------------------|

| 1, 2, 3                      | A <sub>0</sub> to A <sub>2</sub>     | address inputs             |

| 4, 5                         | $\overline{E}_1, \overline{E}_2$     | enable inputs (active LOW) |

| 6                            | E <sub>3</sub>                       | enable input (active HIGH) |

| 8                            | GND                                  | ground (0 V)               |

| 15, 14, 13, 12, 11, 10, 9, 7 | $\overline{Y}_0$ to $\overline{Y}_7$ | outputs (active LOW)       |

| 16                           | Vcc                                  | positive supply voltage    |

### Decodificador 74 138 – tabela verdade

### 3-to-8 line decoder/demultiplexer; inverting

#### **FUNCTION TABLE**

| INPUTS         |                |                |       |                |                |                  |            | OUT            | PUTS             |                  |                       |                       |            |

|----------------|----------------|----------------|-------|----------------|----------------|------------------|------------|----------------|------------------|------------------|-----------------------|-----------------------|------------|

| E <sub>1</sub> | E <sub>2</sub> | E <sub>3</sub> | $A_0$ | A <sub>1</sub> | A <sub>2</sub> | $\overline{Y}_0$ | <u>Y</u> 1 | ₹ <sub>2</sub> | $\overline{Y}_3$ | $\overline{Y}_4$ | <b>Y</b> <sub>5</sub> | <b>Y</b> <sub>6</sub> | <b>₹</b> 7 |

| Н              | Х              | Х              | Х     | Х              | Х              | Н                | Н          | Н              | Н                | Н                | Н                     | Н                     | Н          |

| X              | Н              | X              | X     | X              | X              | H                | Н          | Н              | Н                | Н                | H                     | Н                     | H          |

| X              | X              | L              | X     | Х              | X              | Н                | Н          | Н              | Н                | Н                | Н                     | Н                     | Н          |

| L              | L              | Н              | L     | L              | L              | L                | Н          | Н              | Н                | Н                | Н                     | Н                     | Н          |

| L              | L              | Н              | Н     | L              | L              | Н                | L          | Н              | Н                | Н                | Н                     | Н                     | H          |

| L              | L              | Н              | L     | Н              | L              | Н                | Н          | L              | Н                | Н                | Н                     | Н                     | н          |

| L              | L              | Н              | Н     | Н              | L              | Н                | Н          | Н              | L                | Н                | Н                     | Н                     | н          |

| L              | L              | Н              | L     | L              | Н              | Н                | Н          | Н              | Н                | L                | Н                     | Н                     | н          |

| L              | L              | Н              | Н     | L              | Н              | Н                | Н          | Н              | Н                | Н                | L                     | Н                     | H          |

| L              | L              | Н              | L     | Н              | Н              | Н                | Н          | Н              | Н                | Н                | Н                     | L                     | Н          |

| L              | L              | Н              | Н     | Н              | Н              | Н                | Н          | Н              | Н                | Н                | Н                     | Н                     | L          |

#### Notes

- 1. H = HIGH voltage level

- L = LOW voltage level

- X = don't care

### Decodificadores

### Exemplo

Implemente um decodificador 4-> 16 a partir de decodificadores 2->4 do tipo descrito abaixo:

| G2 | G1 | Α | В | Y0 | Y1 | Y2 | Y3 |

|----|----|---|---|----|----|----|----|

| 1  | Х  | Х | Х | 1  | 1  | 1  | 1  |

| Х  | 0  | Х | Х | 1  | 1  | 1  | 1  |

| 0  | 1  | 0 | 0 | 0  | 1  | 1  | 1  |

| 0  | 1  | 0 | 1 | 1  | 0  | 1  | 1  |

| 0  | 1  | 1 | 0 | 1  | 1  | 0  | 1  |

| 0  | 1  | 1 | 1 | 1  | 1  | 1  | 0  |

G1 e G2 são controles que habilitam a saída. A saída Y0-Y3 selecionada fica em '0'. As demais ficam em '1'.

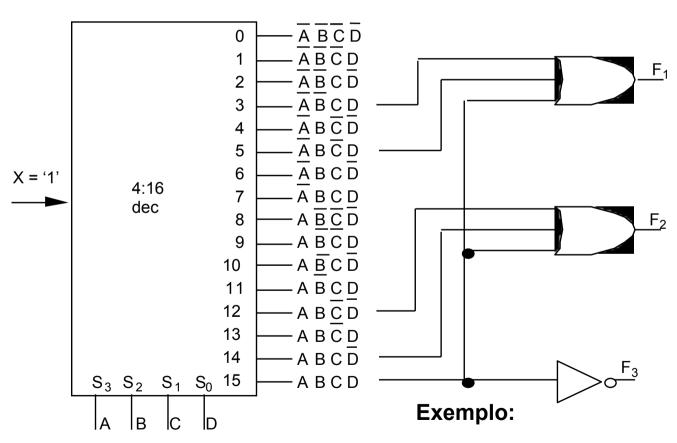

## Decodificadores/demultiplexadores

■ Decodificadores como gerador de funções

F1 = A' B C' D + A' B' C D + A B C D F2 = A B C' D' + A B C F3 = (A' + B' + C' + D')