# Aprendendo a utilizar a Ferramenta Modelsim

GRUPO DE ENGENHARIA DA COMPUTAÇÃO

Professor: Lucas Cambuim (lfsc) Adaptado por : Lucas Amorim, Matheus Costa e Anderson

Henrique

• É um simulador computacional para análise de sistemas digitais

Possui alta fidelidade de resultados

#### Possui alta fidelidade de resultados

os resultados obtidos na simulação refletem fielmente os resultados reais do circuito rodando na FPGA.

Atualmente é o simulador de sistemas digitais mais aceito tanto pelo mundo acadêmico como pela indústria.

- Mais rápido para simular e corrigir o seu código

- Tempo de compilação é muito menor do que o tempo de síntese em plataforma.

Suporta a linguagem SystemVerilog entre outras linguagens

• Oferece diversas maneiras de encontrar erros de código.

- Permite inserir características físicas reais do circuito digital no código.

- Inserção de tempo de propagação de sinal

Manuseio por IDE gráfica ou scripts.

#### Obtendo a ferramenta

#### Site da altera:

https://www.intel.com/content/www/us/en/progra mmable/downloads/download-center.html

#### Nos computadores do CIn:

Pesquisar por: ModelSim - INTEL FPGA STARTER EDITION 10.6d

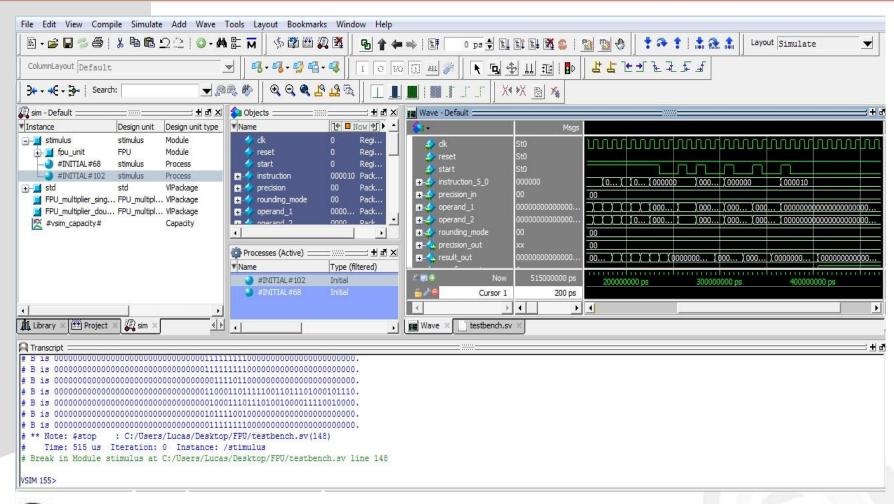

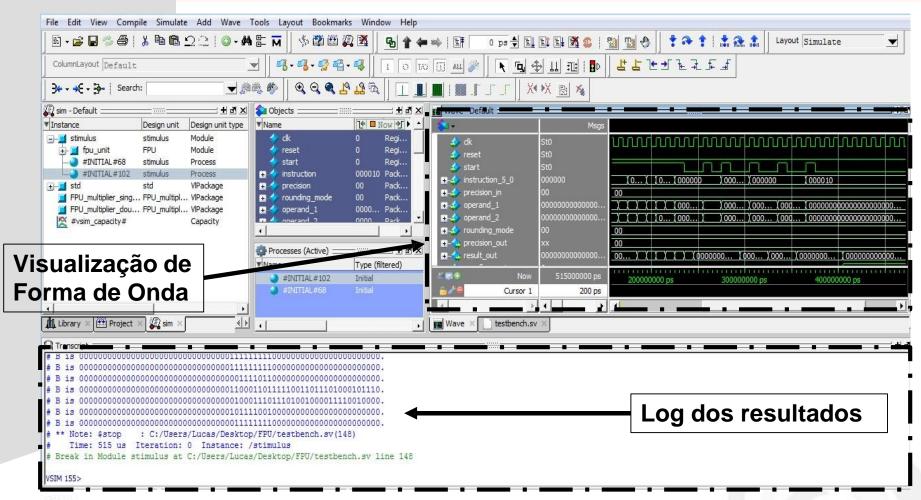

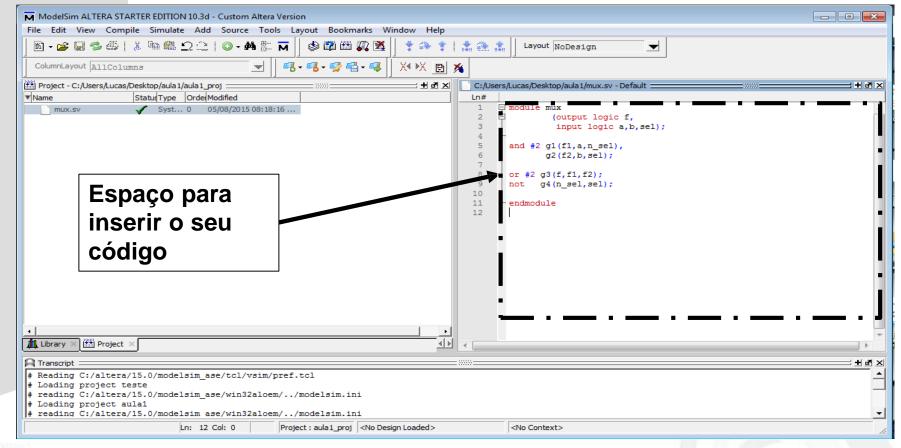

### Visão da Ferramenta

### Recursos importantes da Ferramenta

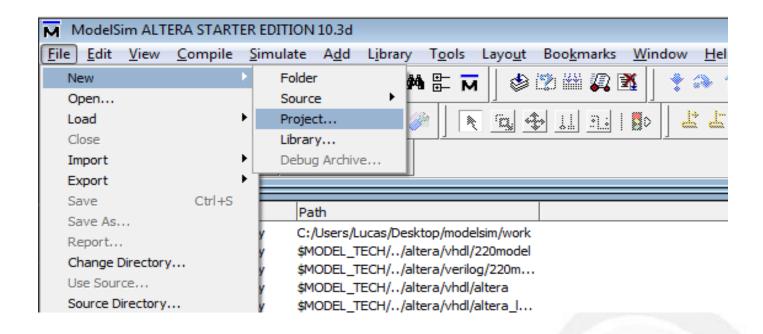

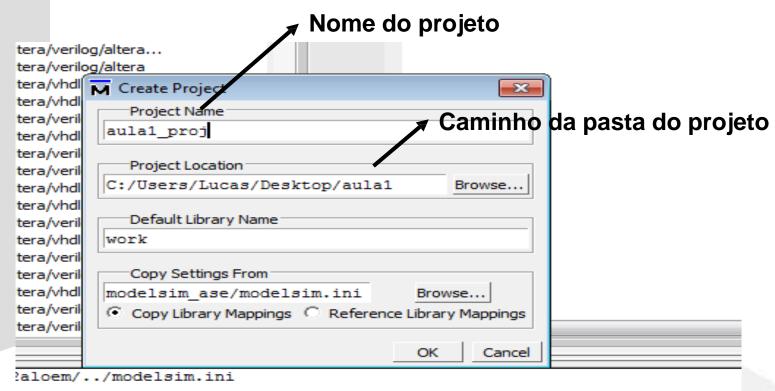

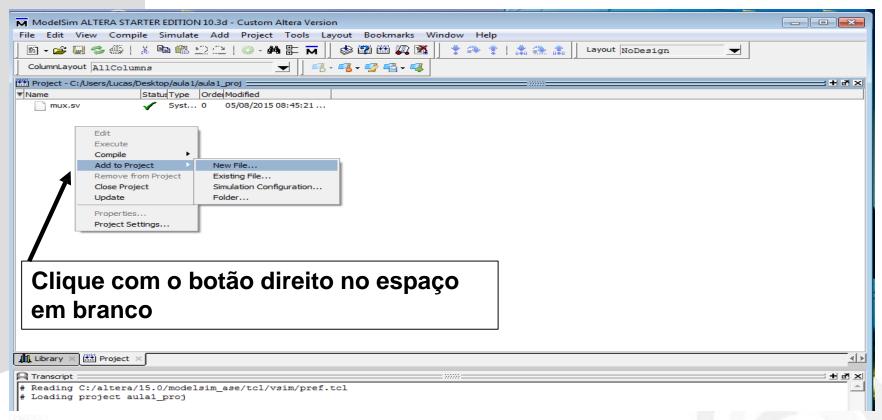

Criando um projeto

(vá em File > new > Project)

#### 1) Criando um projeto

!aloem/../modelsim.ini

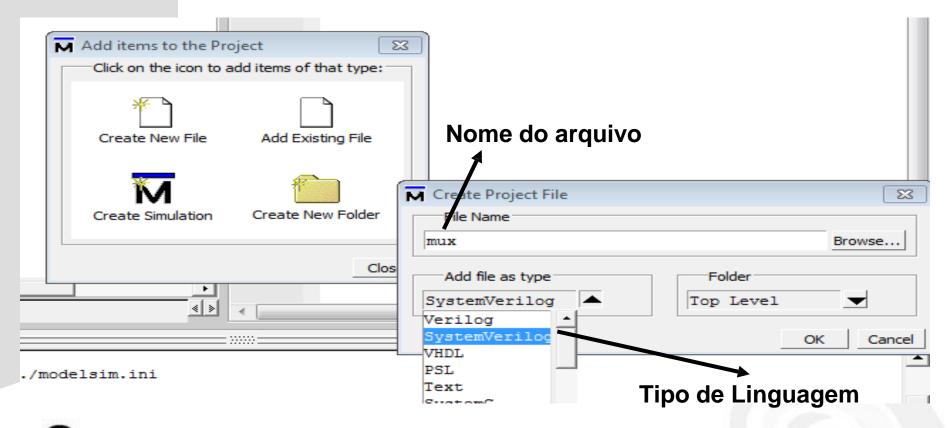

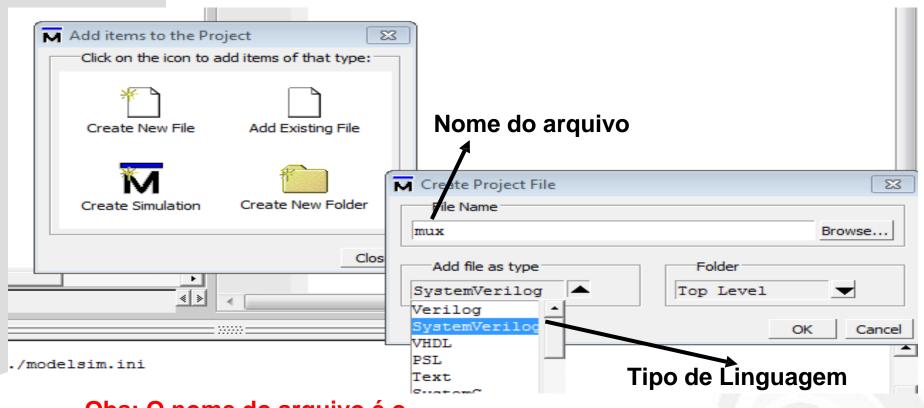

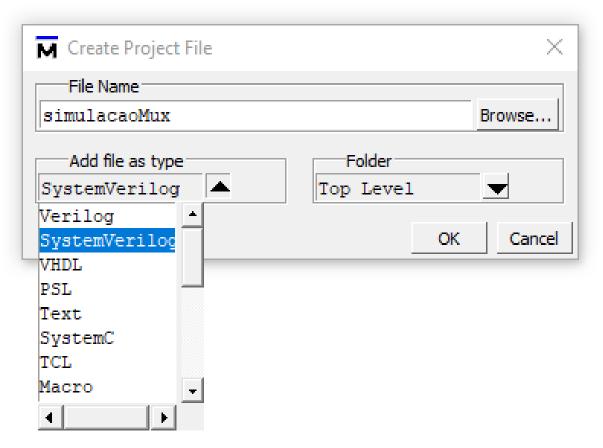

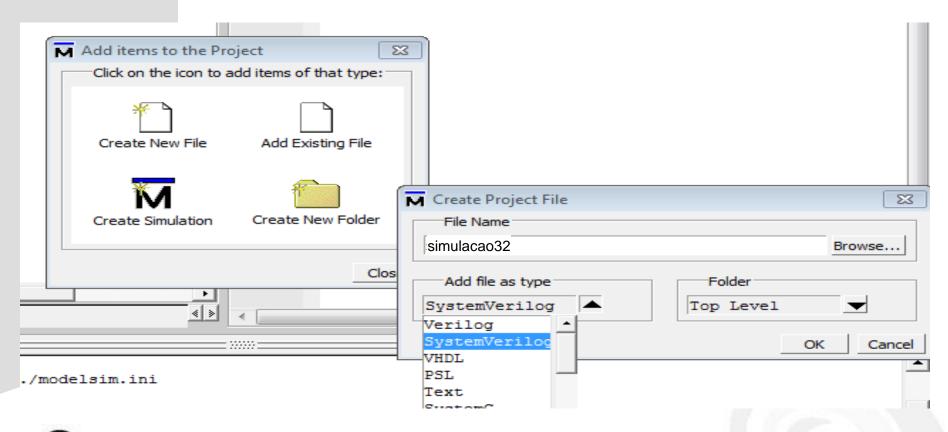

2) Criando uma implementação em System Verilog

Obs: O nome do arquivo é o

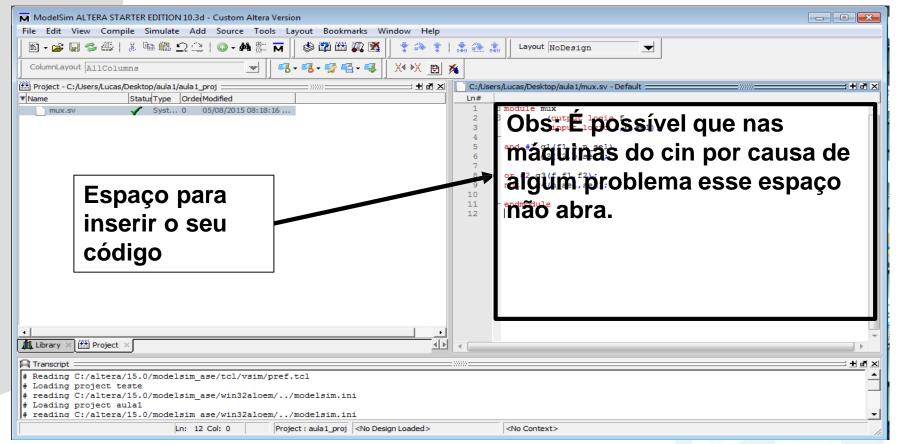

2) Criando uma implementação em System Verilog

Mas, não tem problema. Você pode usar o notepad++ ou qualquer ferramenta de edição de código em SystemVerilog.

```

C:\Users\lfsc\Desktop\aula1\mux.sv - Notepad++

File Edit Search View Encoding Language Settings Tools Macro Run Plugins Window ?

**The Macro

```

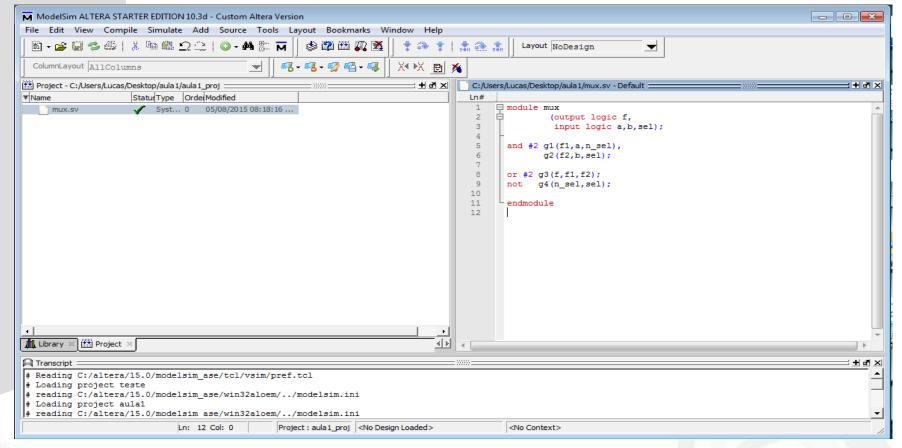

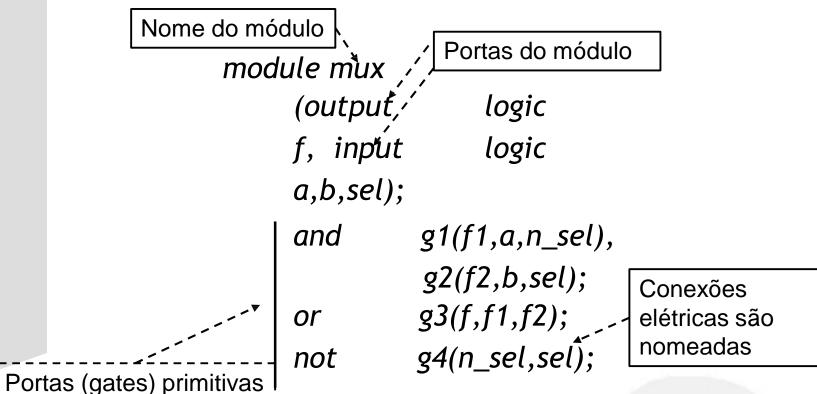

#### 2) Criando uma implementação em System Verilog

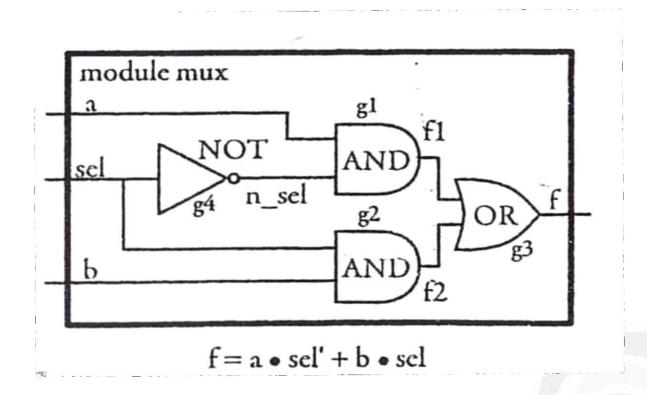

module mux (output logic f, input logic a,b,sel); and g1(f1,a,n\_sel), *g*2(*f*2,*b*,*sel*); g3(f,f1,f2);or *g*4(n\_*sel*,*sel*); not

Copie este código exemplo e cole no arquivo mux.sv

endmodule: mux

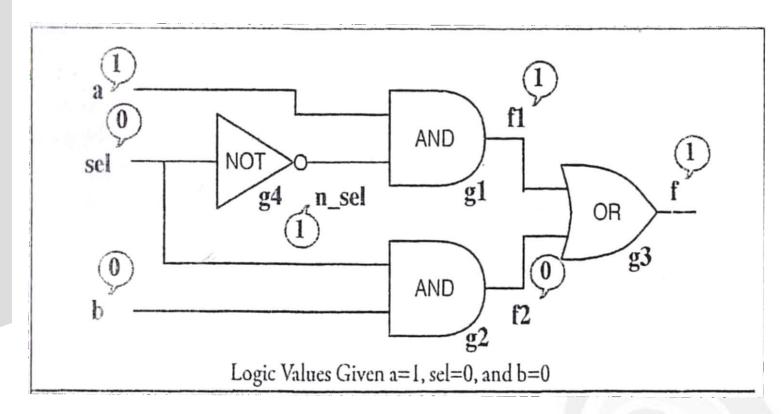

#### 2) Criando uma implementação System Verilog

são instanciadas e

nomeadas

*lendmodule*

Visão em nível de portas lógicas desta implementação

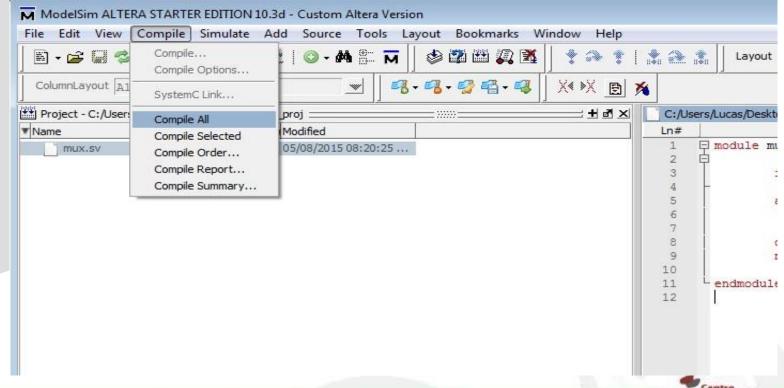

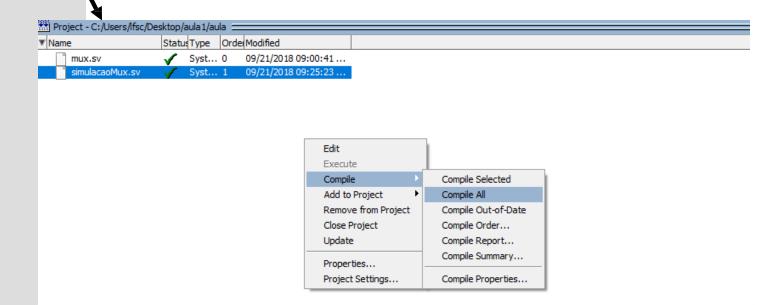

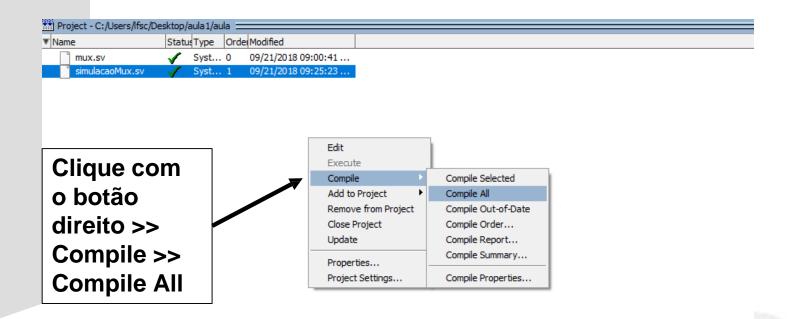

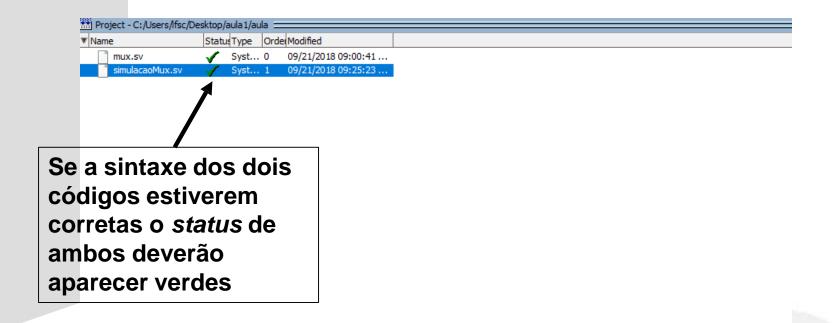

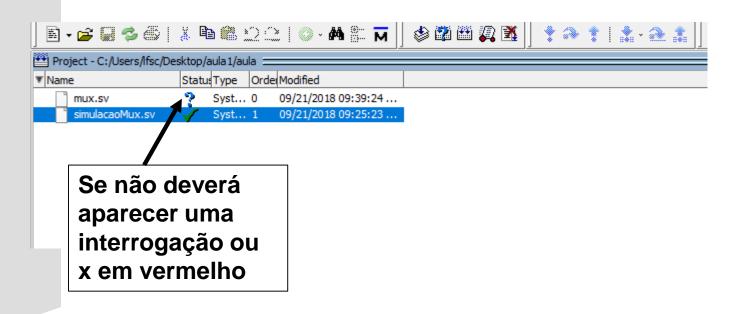

3) Compilando todos os códigos do projeto (vá em Compile > compile all)

O que falta para podermos simular o código

O que falta para podermos simular o código

?

Gerar algum dado de entrada

O que falta para podermos simular o código

?

...e em seguida verificar a resposta do módulo

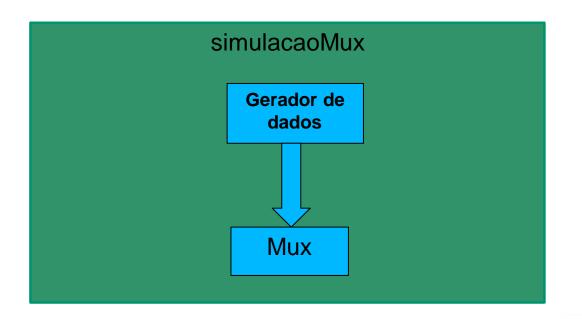

## Exemplo do comportamento do modulo para um dado de entrada

Ilustração do modulo gerador de sinal com o módulo que será testado

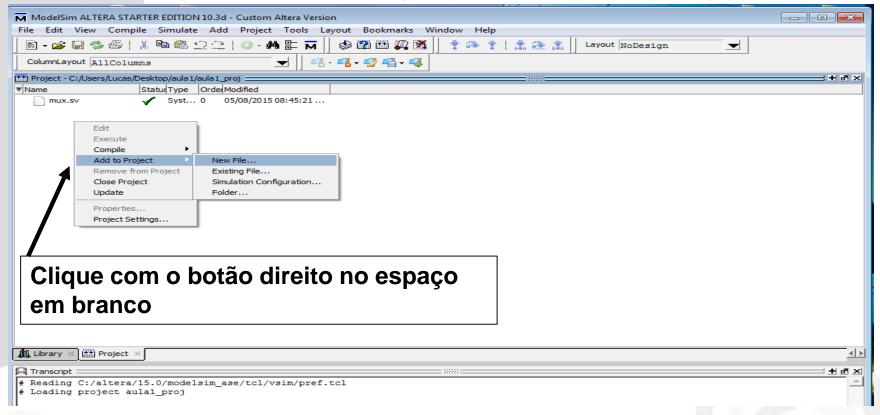

4) Adicionando um novo arquivo .sv que contem o código para geração de dados de entrada

## 4) Adicionando um novo arquivo .sv que contem o código para geração de dados

```

module simulacaoMux; Cria uma instância do módulo mux e chamando de dut

mux dut(.f(muxOut), .a(count[2]), .b(count[1]), .sel(count[0]));

initial begin

$monitor($time,"a b sel = %b, muxOut = %b", count, muxOut);

for(count = 0; count != 3'b111; count++) #10;

#10 $stop;

end

```

## 4) Adicionando um novo arquivo .sv que contem o código para geração de dados

```

module simulacaoMux;

logic [2:0]count;

logic muxOut;

mux dut(.f(muxOut), .a(count[2]), .b(count[1]), .sel(count[0]));

initial begin

$monitor($time,"a b sel = %b, muxOut = %b", count, muxOut);

for(count = 0; count != 3'b111; count++) #10;

#10 $stop;

end

```

Centro de Informática

#### Entendendo o código de geração de dados

#### Initial

É executado apenas uma vez no início da simulação. É tipicamente usado para inicializar variáveis e especificar formas de onda de sinais durante a simulação

#### \$monitor

Tira um print dos dados toda vez que um de seus parâmetros mudam

#### #10

Solicita que o simulador pare sua execução por 10 unidades de tempo.

```

initial begin

$monitor($time,"a b sel = %b, muxOut = %b",

count, muxOut);

for(count = 0; count != 3'b111; count++) #10;

#10 $stop;

end

```

#### \$stop

Termina a simulação

Dê um compile All

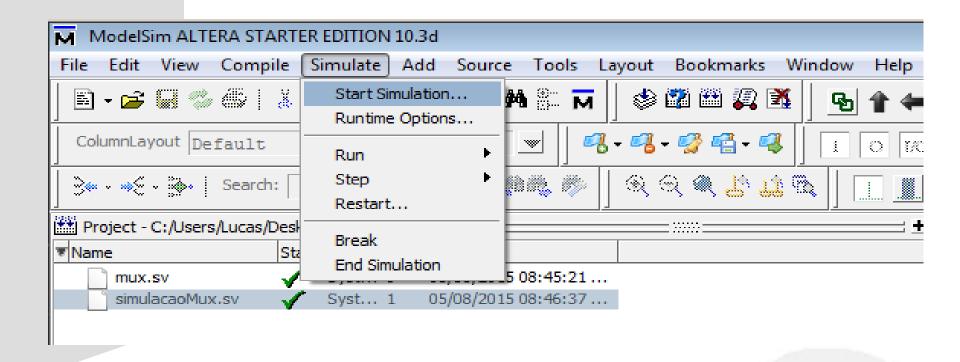

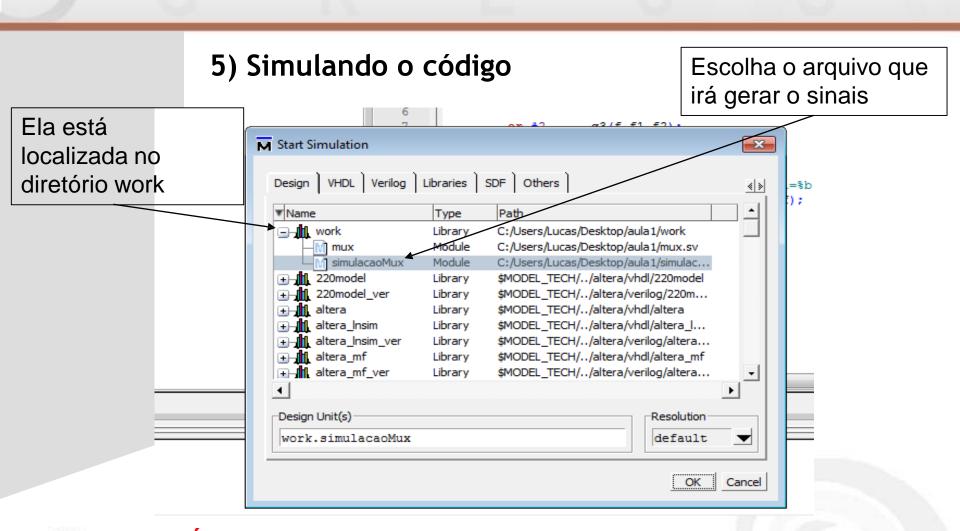

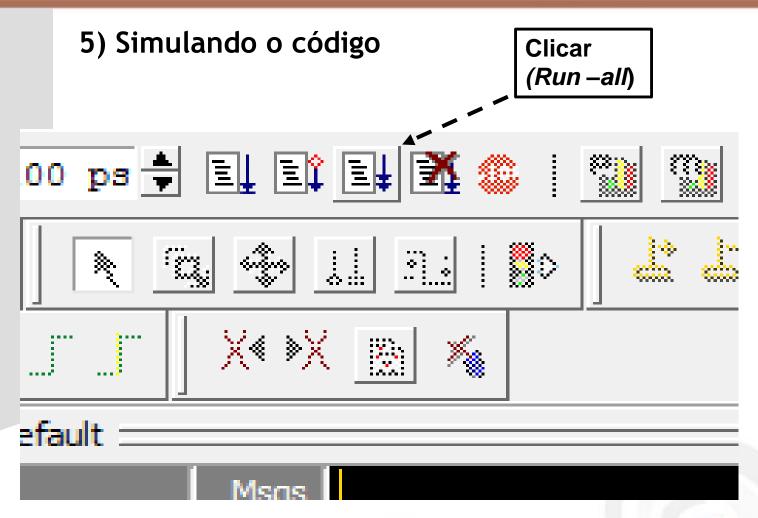

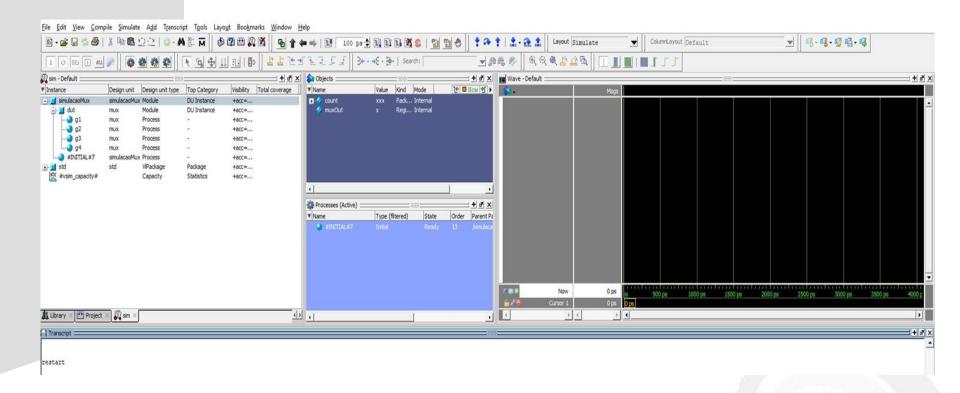

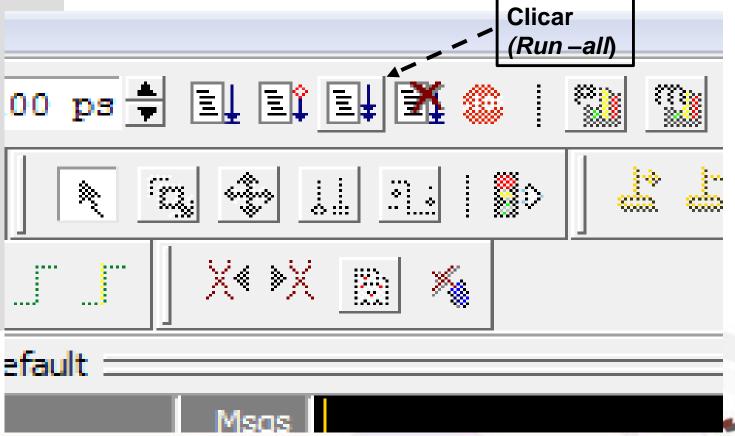

#### 5) Simulando o código

Dica: É o modulo top que chama todos os outros módulos

#### 5) Simulando o código

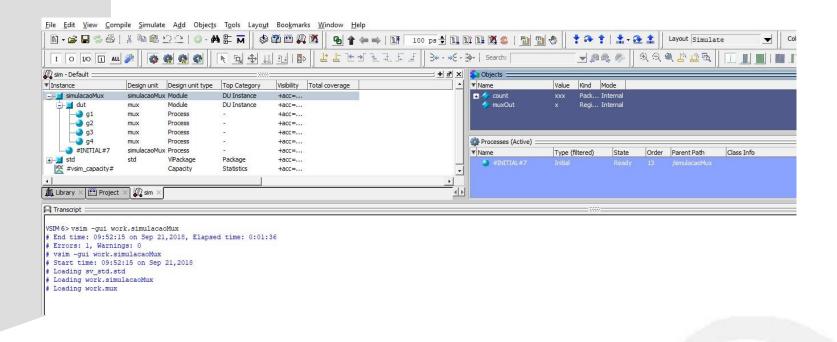

#### 5) Simulando o código

```

└-◇ #INITIAL#7

simulacaoMux Process

+acc=...

VIPackage

Package

+acc=...

#vsim_capacity#

Statistics

Capacity

+acc=...

🎉 sim 🗵

Project

Transcript

VSIM 11> run -all

0a b sel = 000, muxOut = 0

Log de

10a b sel = 001, muxOut = 0

20a b sel = 010, muxOut = 0

simulação

30a \ b \ sel = 011, \ muxOut = 1

40a \ b \ sel = 100, \ muxOut = 1

50a b sel = 101, muxOut = 0

60a b sel = 110, muxOut = 1

70a \ b \ sel = 111, \ muxOut = 1

: C:/Users/lfsc/Desktop/aulal/simulacaoMux.sv(10)

Time: 80 ps Iteration: 0 Instance: /simulacaoMux

# Break in Module simulacaoMux at C:/Users/lfsc/Desktop/aulal/simulacaoMux.sv line 10

```

OBS: Sempre que você alterar o seu código você precisará compilar todos os arquivos modificados e simular novamente.

OBS: Se você alterar o arquivo e não compilar e em seguida simular, a simulação ocorrerá baseada na última compilação válida.

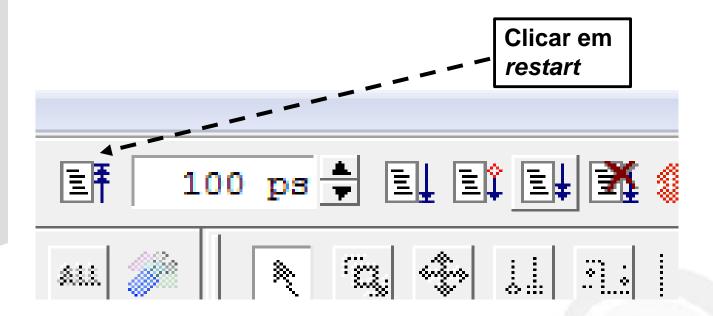

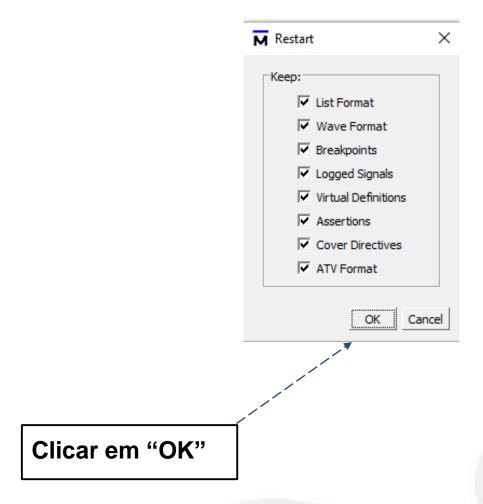

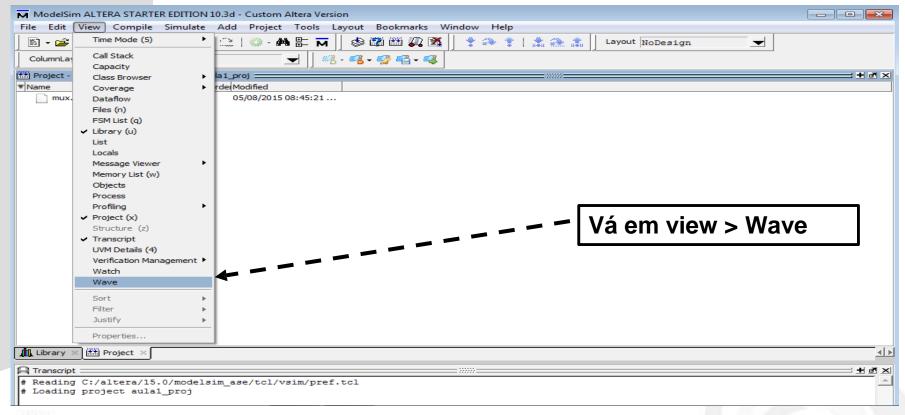

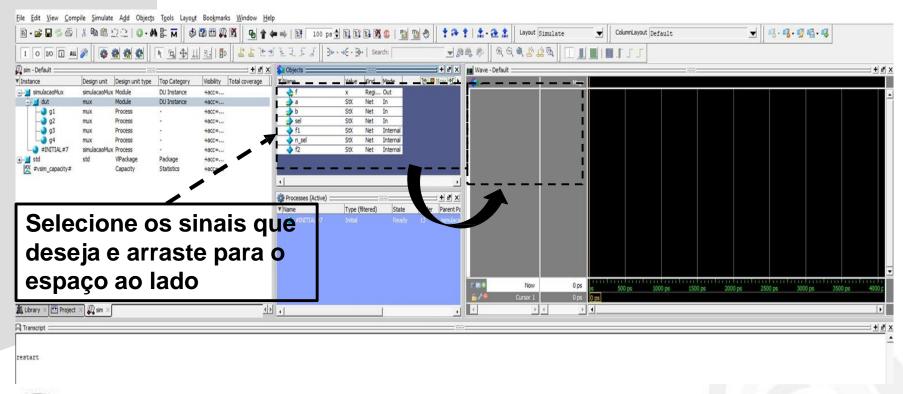

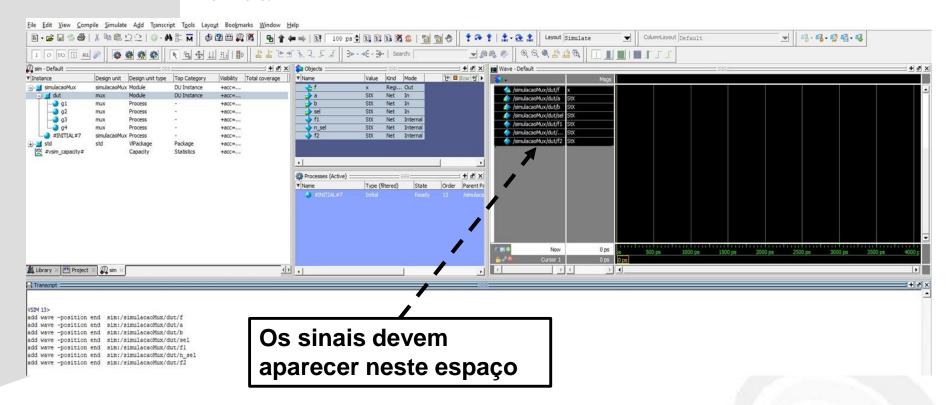

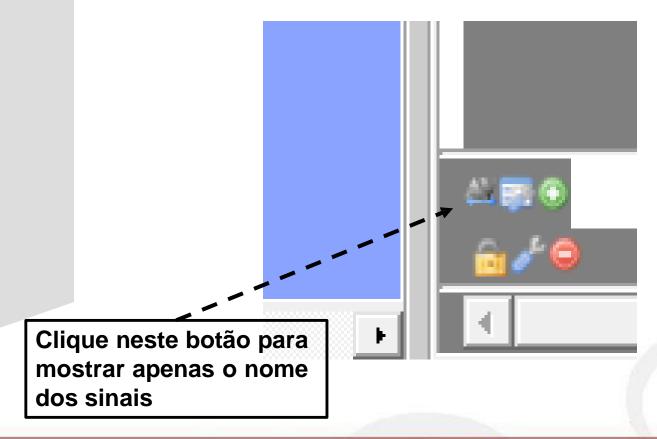

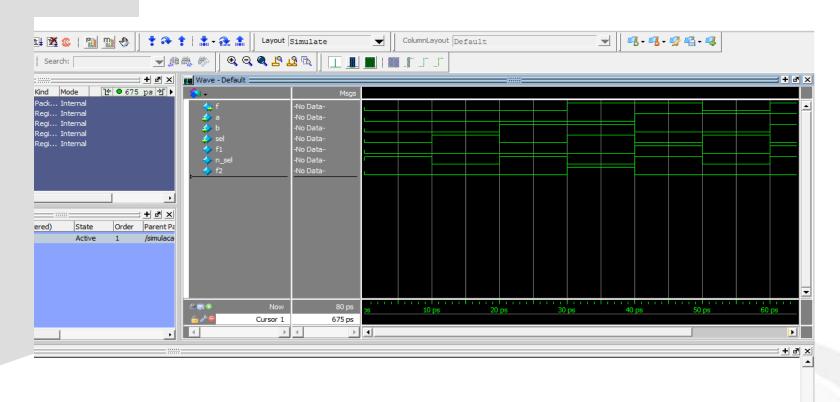

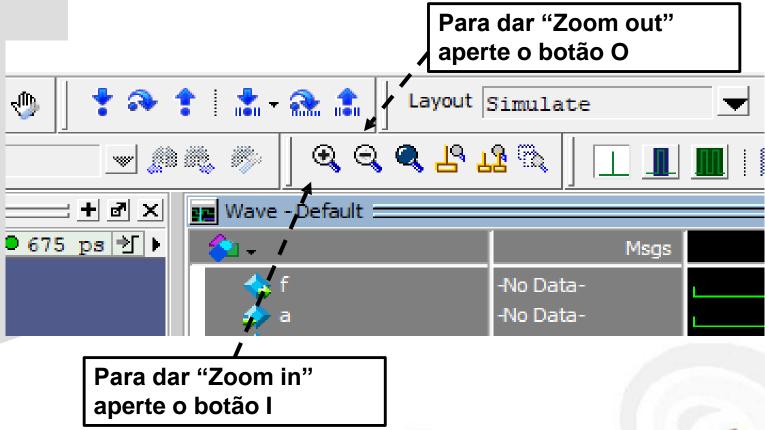

6) Repetindo a simulação e inserindo forma de onda (Waveform)

#### Memória utilizada para armazenar as instruções

#### Inicializando dados na memória

```

DEPTH = 8;

-- The size of memory in words

-- The size of data in bits

WIDTH = 8;

ADDRESS_RADIX = DEC; -- The radix for address values

DATA_RADIX =

-- The radix for data values

BIN; CONTENT

-- start of (address : data pairs)

BEGIN

000: 00000000;

001: 10100111;

002: 00011000;

003: 00100000;

004:00000001;

005:00001001;

006:00111000;

007:00100010;

END;

```

Estrutura de código para inicializar os dados em memória.

DEPTH = 8;

WIDTH = 8;

002: 00011000;

003: 00100000;

004: 00000001;

005: 00001001;

006: 00111000;

007: 00100010;

END;

#### Inicializando dados na memória

```

ADDRESS_RADIX = DEC; -- The radix for address values

DATA_RADIX = -- The radix for data values

BIN; CONTENT -- start of (address : data pairs)

BEGIN

Maneira como

deve ser

DATA_RADIX = -- The radix for data values

-- start of (address : data pairs)

BEGIN

000: 000000000;

001: 10100111;

```

-- The size of data in bits <

endereços. DEC – decimal, BIN - Binário

descritos os

Maneira como deve ser descritos os dados. DEC – decimal, BIN - Binário

-- The size of memory in words ◀**- - Quantidade de palavras**

#### Inicializando dados na memória

```

DEPTH = 8;

-- The size of memory in words

-- The size of data in bits

WIDTH = 8;

ADDRESS_RADIX = DEC; -- The radix for address values

DATA_RADIX =

-- The radix for data values

BIN; CONTENT

-- start of (address : data pairs)

BEGIN

Início do

000: 00000000;

conteúdo em

001: 10100111;

memória

002: 00011000;

003: 00100000;

004: 00000001;

005: 00001001;

006: 00111000;

007: 00100010;

Fim do

conteúdo em

memória

```

#### Inicializando dados na memória

```

DEPTH = 8;

-- The size of memory in words

-- The size of data in bits

WIDTH = 8;

ADDRESS_RADIX = DEC; -- The radix for address values

DATA_RADIX =

-- The radix for data values

BIN; CONTENT

-- start of (address : data pairs)

BEGIN

000: 00000000;

001: 10100111;

002: 00011000;

003: 00100000;

004: 00000001;

005: 00001001;

006: 00111000;

007: 00100010;

END;

```

Esse código tem que ser salvo exatamente com o nome instructions.mif

Baixe o arquivo "projeto.zip"

Localizado em:

https://github.com/leamorim/Infra-de-Hardware-EC-CIn-UFPE/blob/master/Aula%20Modelsim/projeto.zip

E Descompacte

Vá na pasta projeto/módulos e copiem os seguintes arquivos:

ramOnChip32.v e Memoria32.sv

para a pasta do seu projeto do modelsim.

Também vá na pasta projeto/modelsim e copie o arquivo

instructions.mif

para a pasta do seu projeto do modelsim.

- O arquivo ramOnChip32.v contém um módulo genérico de memória

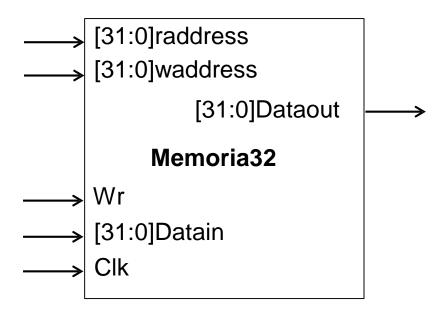

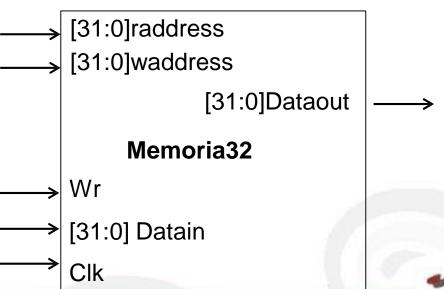

- O arquivo Memoria32.sv implementa sobre ramOnChip32.v o módulo de memória de 32 bits com as entradas e saídas mapeadas da seguinte forma:

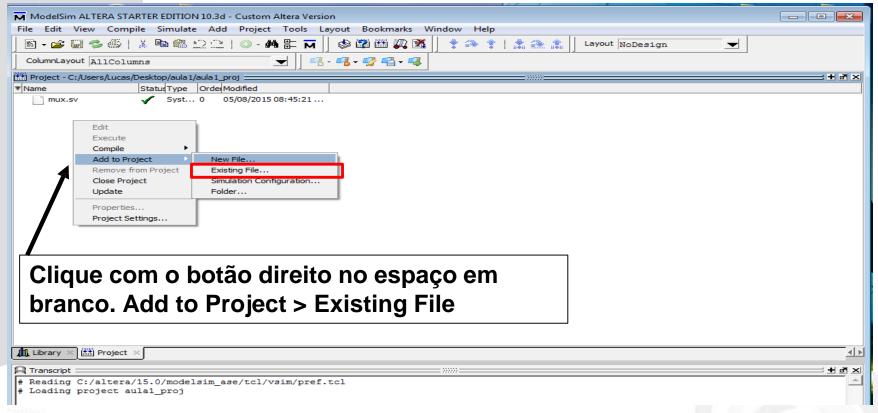

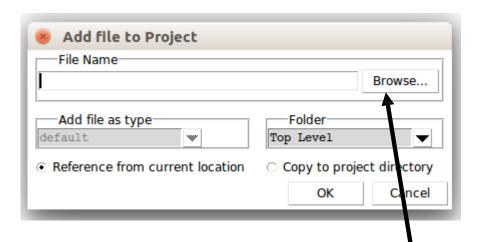

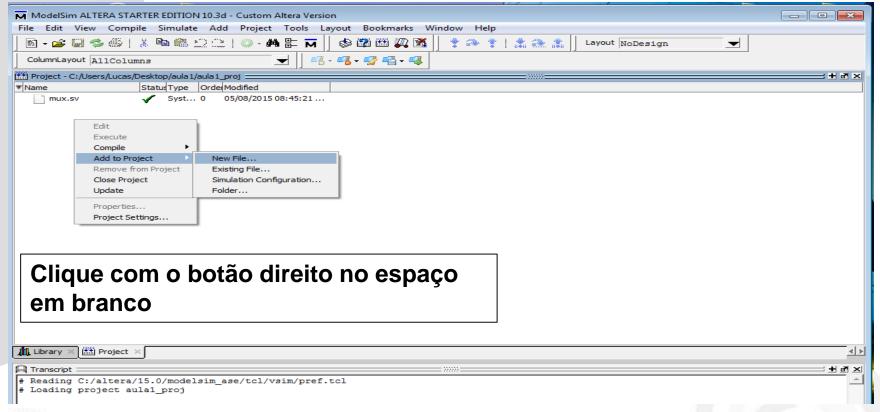

#### Adicionando módulos existentes

#### Adicionando módulos existentes

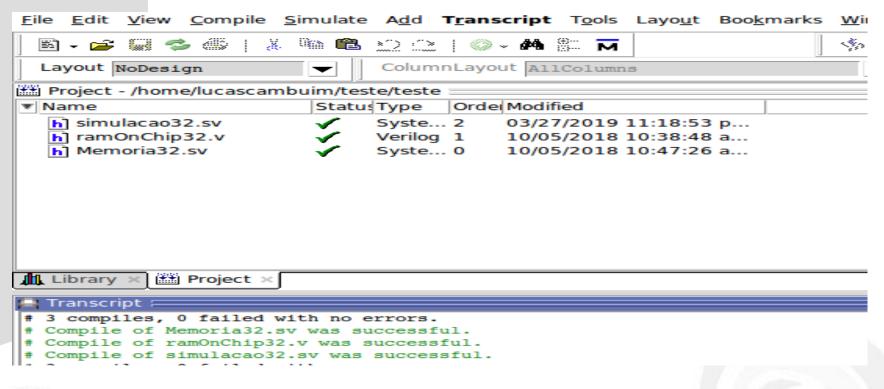

Selecione os dois arquivos ramOnChip32.v e Memoria32.sv

# Agora crie um módulo novo que será aquele que irá gerar os dados para a

#### Dê o nome de simulação 32

Digite o seguinte código no arquivo simulacao32 (também disponível em projeto/modulos)

```

`timescale 1ps/1ps

module simulacao32;

logic clk;

logic nrst;

reg [31:0]rdaddress;

reg [31:0]wdaddress;

reg [31:0]data;

reg Wr;

wire [31:0]q;

```

Digite o seguinte código no arquivo simulacao32 (também disponível em projeto/modulos)

```

`timescale 1ps/1ps

module simulacao32;

logic clk;

logic nrst;

reg [31:0]rdaddress;

reg [31:0]wdaddress;

reg [31:0]data;

reg Wr;

wire [31:0]q;

Criação de fios

e registradores

```

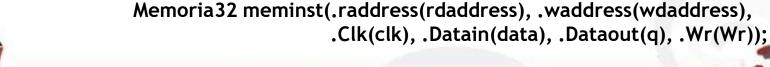

Memoria32 meminst(.raddress(rdaddress), .waddress(wdaddress), .Clk(clk), .Datain(data), .Dataout(q), .Wr(Wr));

```

`timescale 1ps/1ps

module simulacao32;

logic clk;

logic nrst;

reg [31:0]rdaddress;

reg [31:0]wdaddress;

reg [31:0]data;

Instanciando o módulo memoria32

reg Wr;

e dando o nome da instancia de

wire [31:0]q;

meminst

Memoria 32 meminst(.raddress(rdaddress),.waddress(wdaddress),

.Clk(clk), .Datain(data), .Dataout(q), .Wr(Wr));

```

```

`timescale 1ps/1ps

module simulacao32;

logic clk;

logic nrst;

reg [31:0]rdaddress;

Conectando os fios e

reg [31:0]wdaddress;

registradores externos as portas

do módulo instanciado

reg [31:0]data;

reg Wr;

wire [31:0]q;

Memoria32 meminst(.raddress(rdaddress), .waddress(wdaddress),

.Clk(clk), .Datain(data), .Dataout(q), .Wr(Wr));

```

```

//gerador de clock e reset

localparam CLKPERIOD = 10000;

localparam CLKDELAY = CLKPERIOD / 2;

initial

begin

clk = 1'b1;

nrst = 1'b1:

#(CLKPERIOD)

#(CLKPERIOD)

#(CLKPERIOD)

nrst = 1'b0;

end

always #(CLKDELAY) clk = ~clk;

```

```

//realiza a leitura

always_ff @(posedge clk or posedge nrst)

begin

if(nrst) rdaddress <= 0;</pre>

else begin

if(rdaddress < 64) rdaddress <= rdaddress + 4;</pre>

else begin

rdaddress <= 0;

$stop;

end

end

end

endmodule

```

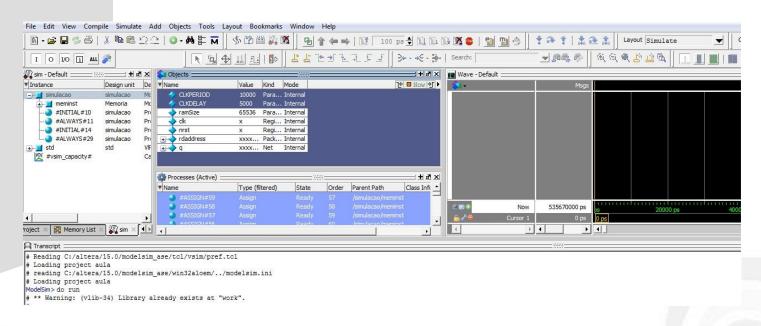

Em seguida vá em Compile > compile All para compilar todos os módulos.

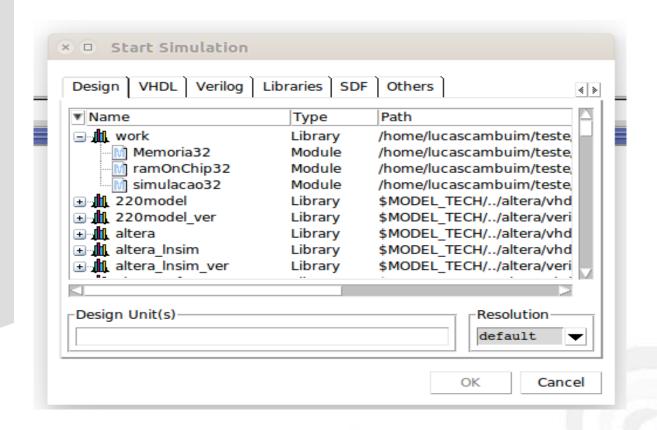

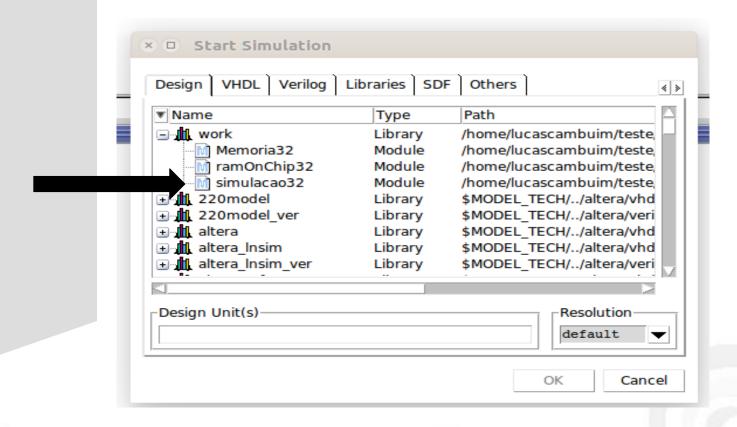

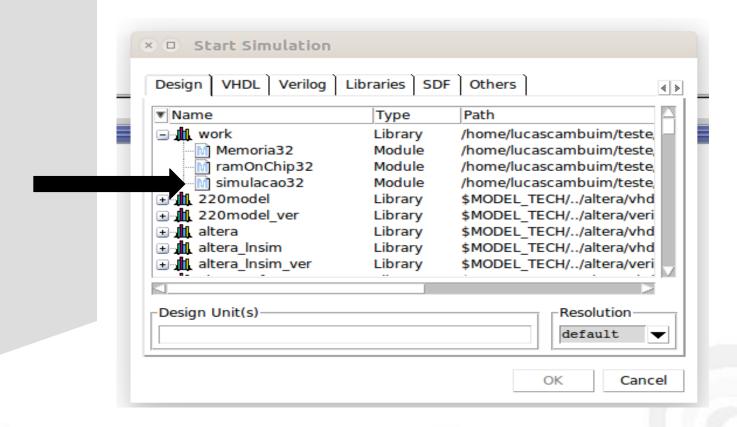

#### Em seguida vá em Simulate > Start Simulate

Na abaLibraries, adiciona a biblioteca "altera\_mf\_ver" para reconhecer a memória

| Add    |

|--------|

| Modify |

| Delete |

|        |

| Add    |

| Modify |

| Delete |

|        |

#### Na aba Design, selecione simulacao32

#### Na aba Design, selecione simulacao32

## Na aba Design, selecione simulacao32

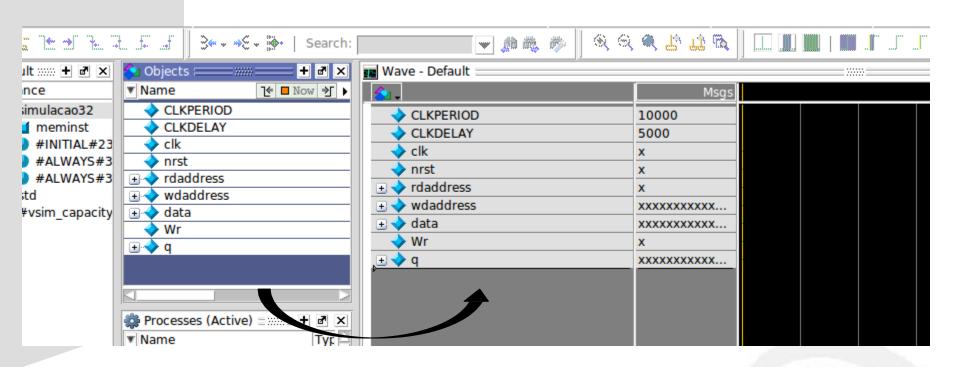

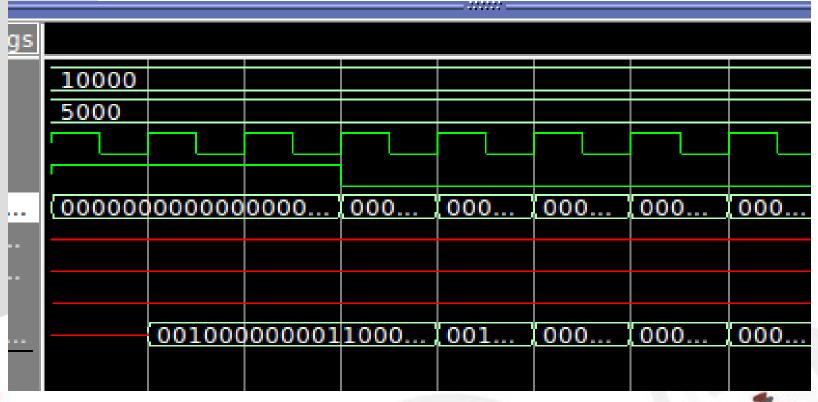

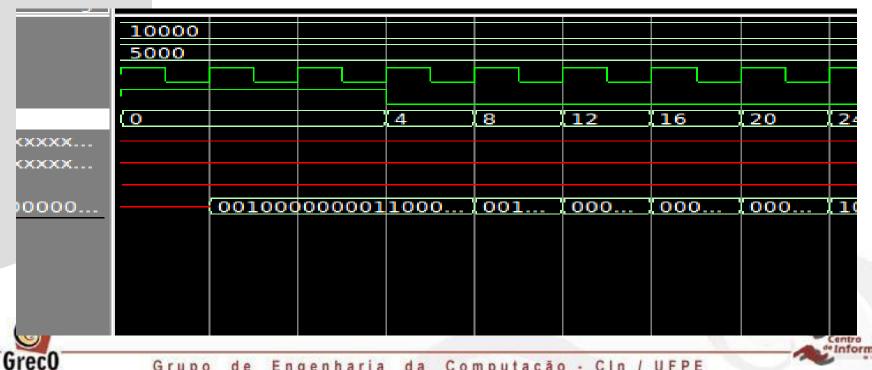

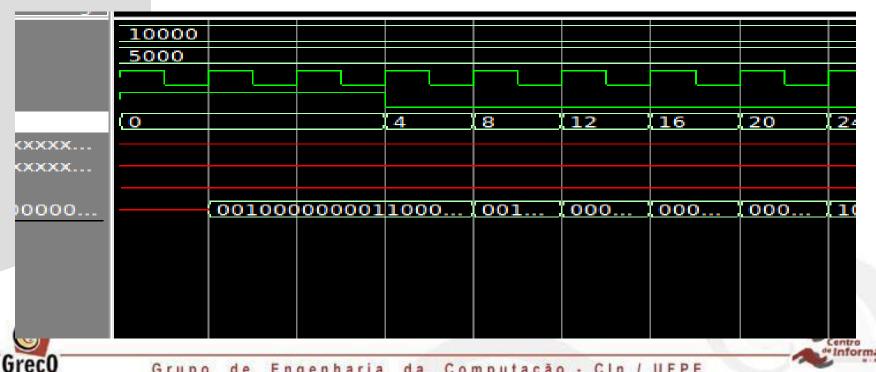

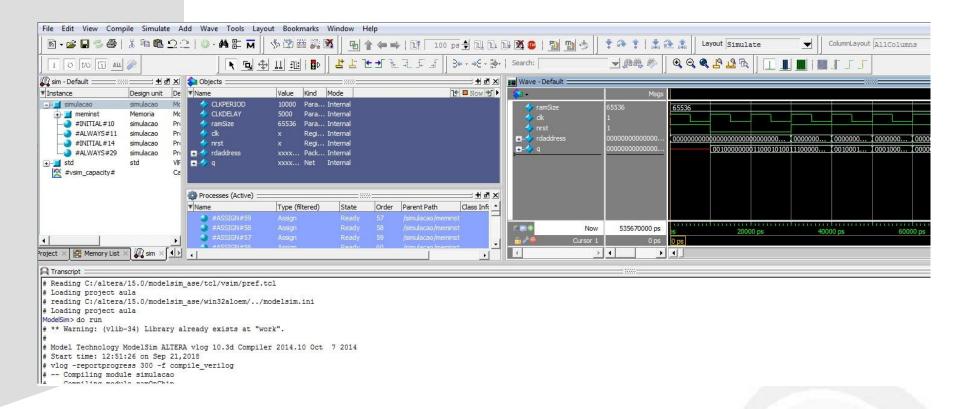

E por fim, clique em run -All e espera o simulador terminar

É possível mudar a forma do número apresentado.

Para isso, clique com o botão direito em cima do sinal desejado, vá em Radix e escolha decimal.

Verifique se a saída da memória está igual aos valores definidos no arquivo instructions.mif

7) Usando memória e script do modelsim

Vamos agora executar um script de modelsim que realiza todos os passos de compilação e simulação de maneira automática para simular a memória.

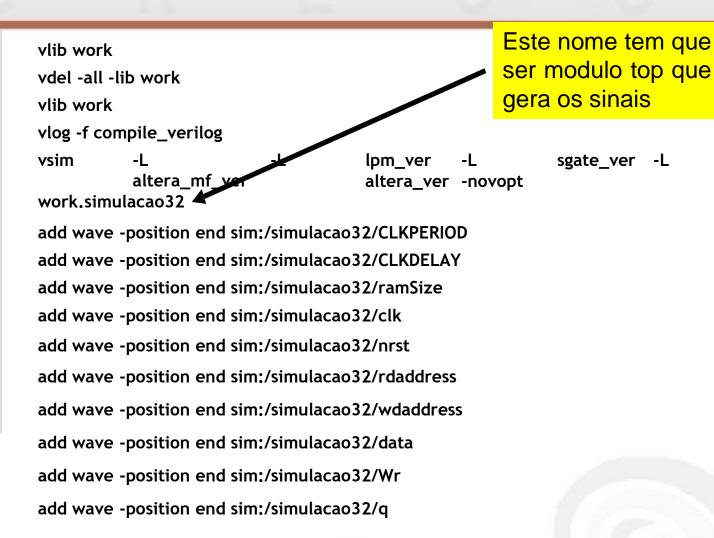

7) Usando memória e script do modelsim

Estrutura de arquivos do "projeto.zip"

| /projeto         |

|------------------|

| /modulos         |

| /ramOnChip32.v   |

| /Memoria32.sv    |

| /simulacao32.sv  |

| /modelsim        |

| /compile_verilog |

| /run             |

| /instruceo mif   |

7) Usando memória e script do modelsim

São dois arquivos de simulação:

a) compile\_verilog

Contém a localização dos arquivos verilog que pertence ao seu projeto.

#### Ex:

- ../modulos/ramOnChip32.v

- ../modulos/Memoria32.v

- ../modulos/simulacao32.sv

7) Usando memória e script do modelsim

São dois arquivos de simulação:

b) runmemoria32

Contém os comandos para compilar e simular no modelsim.

```

vlib work

vdel -all -lib work

vlib work

vlog -f compile_verilog

lpm ver

sgate ver -L

vsim

altera mf ver

altera ver -novopt

work.simulacao32

add wave -position end sim:/simulacao32/CLKPERIOD

add wave -position end sim:/simulacao32/CLKDELAY

add wave -position end sim:/simulacao32/ramSize

add wave -position end sim:/simulacao32/clk

add wave -position end sim:/simulacao32/nrst

add wave -position end sim:/simulacao32/rdaddress

add wave -position end sim:/simulacao32/wdaddress

add wave -position end sim:/simulacao32/data

add wave -position end sim:/simulacao32/Wr

add wave -position end sim:/simulacao32/q

```

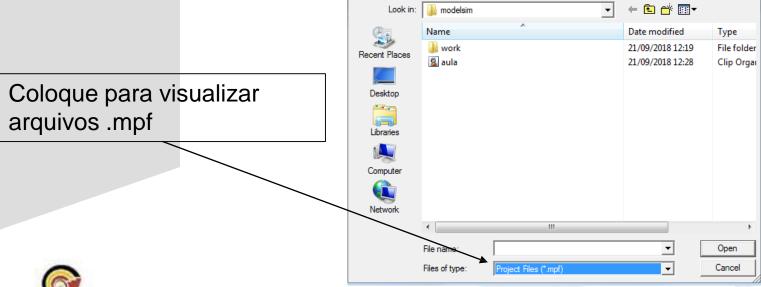

- 7) Usando memória e script do modelsim

- Abra o modelSim

- 2. Clique em File > open

- 3. Localize o arquivo projeto/modelsim/projeto.mpf

7) Usando memória e script do modelsim

Digite no espaço "transcript" o seguinte comando:

do runmemoria32

#### Transcript

- # Reading C:/altera/15.0/modelsim\_ase/tcl/vsim/pref.tcl

- # Loading project aula

- # reading C:/altera/15.0/modelsim ase/win32aloem/../modelsim.ini

- # Loading project aula

ModelSim > do runmemoria32

#### 7) Usando memória e script do modelsim

7) Usando memória e script do modelsim

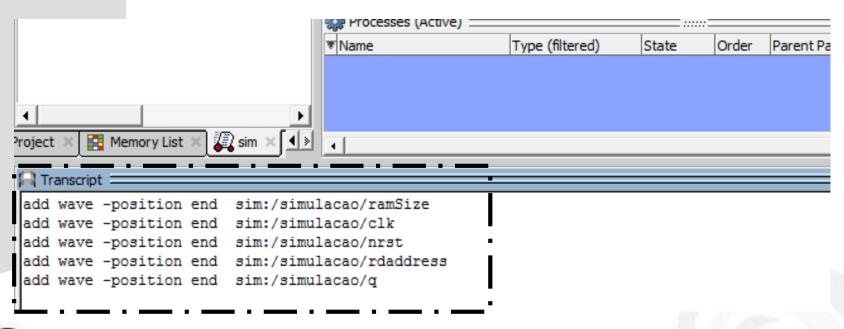

Se quiser adicionar sinais ao script 1°) Adicione manualmente

7) Usando memória e script do modelsim

Se quiser adicionar sinais ao script 2°) Copie os comandos

#### 7) Usando memória e script do modelsim

Se quiser adicionar sinais ao script 3°) Cole no arquivo run

• • •

vsim -L altera\_mf\_ver -L lpm\_ver -L sgate\_ver -L altera\_ver -novopt work.simulação32

add wave -position end sim:/simulacao32/ramSize add wave -position end sim:/simulacao32/clk add wave -position end sim:/simulacao32/nrst add wave -position end sim:/simulacao32/rdaddress add wave -position end sim:/simulacao32/q

# Comandos para script

- Comandos e diretivas disponíveis no modelsim detalhados no seguinte PDF:

- https://www.microsemi.com/documentportal/doc\_view/136364-modelsim-me-10-4ccommand-reference-manual-for-libero-soc-v11-7

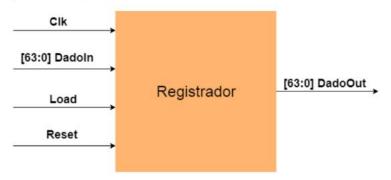

### Exercício

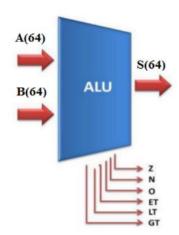

- Usando o módulo register.sv e o módulo ula64.vhd, disponível no arquivo projeto.zip, faça uma máquina de estados que incrementa o valor de uma instância de register.sv de 4 em 4 usando uma instância de ula64.vhd e salve o valor resultante na mesma instância de register.sv

- Observação: O registrador leva um ciclo para ter o valor escrito disponível

- É recomendado criar um outro arquivo para fazer as conexões

# Exercício - Observações

Obs: o dado que entra em Data\_in só passa para Data\_out quando o registrador passa 1 ciclo de clock com o sinal **Load** ativo (Load = 1).

| Função | Operação      | Descrição       | Flags      |

|--------|---------------|-----------------|------------|

| 000    | S = A         | Carrega A       | Z, N       |

| 001    | S = A + B     | Soma            | Z, N, O    |

| 010    | S = A - B     | Subtração       | Z, N, O    |

| 011    | S = A and $B$ | And lógico      | Z          |

| 100    | S = A + 1     | Incremento de A | Z, N, O    |

| 101    | S = not A     | Negação de A    | Z          |

| 110    | S = A  xor  B | OU exclusivo    | Z          |

| 111    | S = A comp B  | Comparação      | EG, GT, LT |

# Aprendendo a utilizar a Ferramenta Modelsim

GRUPO DE ENGENHARIA DA COMPUTAÇÃO

Professor: Lucas Cambuim (lfsc)

Adaptado por: Lucas Amorim,

Matheus Costa e Anderson

Henrique