cin.ufpe.br

#### Infra-estrutura de Hardware

### AULA SIMULADOR RISC-V / ASSEMBLY RISC-V

#### Roteiro da Aula

- Revisão

- Simulador Venus

- Lista

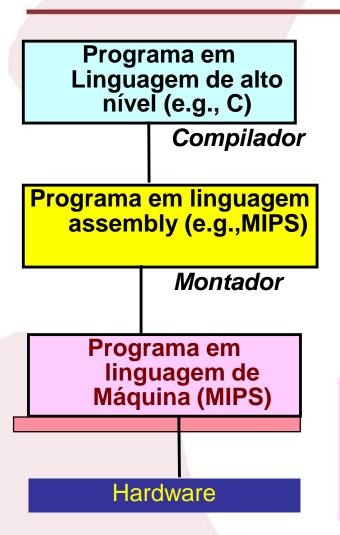

#### Representação da Informação

```

temp = v[k];

v[k] = v[k+1];

v[k+1] = temp;

```

```

Iw $to, 0($2)

Iw $t1, 4($2)

sw $t1, 0($2)

sw $t0, 4($2)

```

```

1000

1100

0100

1000

0000

0000 0000

0000

1000

1100

0100

1001

0000

0000

0000

0100

1010

1100

0100

1001

0000

0000 0000

0000

1100 0100 1000 0000 0000 0000

```

de Informática

# QUAIS INSTRUÇÕES QUE UM PROCESSADOR EXECUTA?

### Conjunto de Instruções (ISA)

- O repertório de instruções de um computador

- Diferentes computadores têm diferentes conjuntos de instruções

- Mas com muitos aspectos em comum

- Os primeiros computadores tinham conjuntos de instruções muito simples

- Implementação simplificada

- Muitos computadores modernos também possuem conjuntos de instruções simples

#### O ISA do RISC-V

- Usado como o exemplo ao longo do livro...

- Desenvolvido na UC Berkeley como ISA aberto

- Agora gerenciado pela Fundação RISC-V (riscv.org)

- Típico de muitos ISAs modernos

- ISAs similares têm uma grande parcela do mercado principal incorporado

- Aplicações em eletrônicos de consumo, equipamentos de rede / armazenamento, câmeras, impressoras, ...

### Operandos em Registradores

- Instruções aritméticas usam operandos de registro

- MIPS possui 32 registradores de 32 bits cada

- Os dados de 32 bits são chamados de "palavra"

- RISC-V possui 32 registradores de 64 bits cada

- Use para dados com acesso frequente

- Os dados de 64 bits são chamados de "palavra dupla"

- 32 registradores de uso geral de 64 bits: x0 a x30

### RISC-V Registradores Centro Contro Co

x0: o valor constante 0

x1: endereço de retorno

x2: apontador de pilha

x3: ponteiro global

x4: ponteiro de linha

x5 - x7, x28 - x31: temporários

x8: ponteiro do quadro

x9, x18 - x27: registros salvos

x10 - x11: argumentos de função / resultados

x12 - x17: argumentos de função

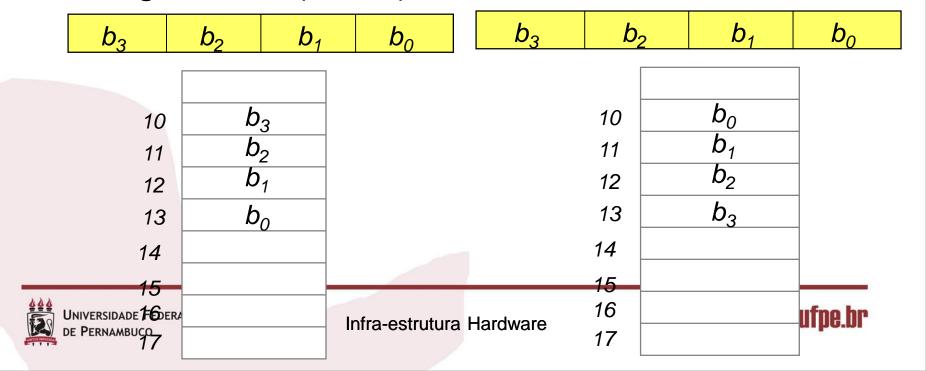

### Operandos na Memória -Endianess

- MIPS/ RISC V

- Inteiros com 32 bits

- Memória endereçada por byte

- Big Endian (MIPS) Little Endian (RISC V x86)

### Operandos na Memória

As únicas instruções que acessam a memória são as instruções de Load e Store

### Operandos Constantes Imediatos

Valores constantes especificados na instrução addi x22, x22, 4

- Implemente o comum de forma eficiente

- Constantes "pequenas" são comuns

- Operandos imediatos evitam instrução de load

### Representando Instruções entro Informática

- As instruções são codificadas em binário

- Código de máquina

- Instruções RISC-V

- Codificadas como instrução de 32 bits

- Pequeno número de formatos e de códigos de operação (opcode),

- números de registradores,...

- Regularidade!

|                         | DICC V                                                                                |  |  |

|-------------------------|---------------------------------------------------------------------------------------|--|--|

| Instrução               | Descrição RISC V                                                                      |  |  |

| nop                     | No operation de Informática                                                           |  |  |

| ld reg, desl(reg_base)  | reg. = mem (reg_base+desl)                                                            |  |  |

| sd reg, desl(reg_base)  | Mem(reg_base+desl) = reg                                                              |  |  |

| lw reg, desl(reg_base)  | reg. (31:0)= mem [reg_base+desl](31:0), extensão do sinal                             |  |  |

| sw reg, desl(reg_base)  | $Mem[reg\_base+desl](31:0) = reg(31:0)$                                               |  |  |

| lh reg, desl(reg_base)  | reg. (15:0)= mem [reg_base+desl](15:0), extensão do sinal                             |  |  |

| sh reg, desl(reg_base)  | $Mem[reg\_base+desl](15:0) = reg(15:0)$                                               |  |  |

| lbu reg, desl(reg_base) | reg. (7:0)= mem [reg_base+desl](7:0), completa com zeros                              |  |  |

| sb (reg, desl(reg_base) | $Mem[reg\_base+desl](7:0) = reg(7:0)$                                                 |  |  |

| add regi, regj,regk     | Regi. <- Regj. + Regk                                                                 |  |  |

| sub regi, regj, regk    | Regi. <- Regj. – Regk                                                                 |  |  |

| and regi, regj,regk     | Regi. <- Regj. and Regk                                                               |  |  |

| addi regi, regj, cte    | Regi = Regj + cte                                                                     |  |  |

| srli regd, regs, n      | Desloca regs para direita n vezes sem preservar sinal, armazena valor deslocado em    |  |  |

|                         | regd                                                                                  |  |  |

| srai regd, regs, n      | Desloca regs para dir. n vezes preservando o sinal, armazena valor deslocado em regd. |  |  |

| slli regd, regs, n      | Desloca regs para esquerda n vezes, armazena valor deslocado em regd.                 |  |  |

| slt regi, regj,regk     | Regi = 1 se (regj) < (regk) caso contrário regi= 0                                    |  |  |

| slti regi, regj,immed   | Regi = 1 se (regj) < extensão sinal de immed, caso contrário regi= 0                  |  |  |

| beq regi, regj, desl    | PC = PC + desl*1  se regi = regj                                                      |  |  |

| bne regi, regj, desl    | PC = PC + desl *1 se regi <> regj                                                     |  |  |

| bge regi, regj, desl    | PC = PC + desl*1 se regi >= regj                                                      |  |  |

| blt regi, regj, desl    | PC = PC + desl*1 se regi < regi                                                       |  |  |

| jal ra,end              | ra = pc, pc = end, se Ra=0 não guarda PC                                              |  |  |

| jalr ra, desl(reg-dst)  | Ra=Pc Pc= reg-dst+desl, se Ra=0 não guarda PC                                         |  |  |

| break                   | Para a execução do programa                                                           |  |  |

Código fonte: <a href="https://github.com/kvakil/venus">https://github.com/kvakil/venus</a>

- Código fonte: <a href="https://github.com/kvakil/venus">https://github.com/kvakil/venus</a>

- Disponível para uso online: <a href="http://www.kvakil.me/venus/">http://www.kvakil.me/venus/</a>

- Suporta o padrão RV32IM.

- <a href="https://riscv.org/specifications/">https://riscv.org/specifications/</a>

- https://rv8.io/isa.html

- Suporta o padrão RV32IM.

- https://www.cl.cam.ac.uk/teaching/1617/ECAD+Arch/files/docs/RISC

VGreenCardv8-20151013.pdf

| Loads    | Load Byte        | I | LB    | rd,rs1,imm   | I           |             |       |

|----------|------------------|---|-------|--------------|-------------|-------------|-------|

|          | Load Halfword    | I | LH    | rd,rs1,imm   |             |             |       |

|          | Load Word        | I | LW    | rd,rs1,imm   | L{D Q}      | rd,rs1,     | imm   |

| Load     | Byte Unsigned    | I | LBU   | rd,rs1,imm   |             |             |       |

| Load     | Half Unsigned    | I | LHU   | rd,rs1,imm   | L{W D}U     | rd,rs1,     | imm   |

| Stores   | Store Byte       | S | SB    | rs1,rs2,imm  |             |             |       |

|          | Store Halfword   | S | SH    | rs1,rs2,imm  |             |             |       |

|          | Store Word       | S | SW    | rs1,rs2,imm  | S{D   Q}    | rs1,rs2     | ,imm  |

| Shifts   | Shift Left       | R | SLL   | rd,rs1,rs2   | SLL{W D}    | rd,rs1,     | rs2   |

| Shift    | Left Immediate   | I | SLLI  | rd,rs1,shamt | SLLI{W   D  | } rd,rs1,   | shamt |

|          | Shift Right      | R | SRL   | rd,rs1,rs2   | SRL{W D}    | rd,rs1,     | rs2   |

| Shift Ri | ight Immediate   | I | SRLI  | rd,rs1,shamt | SRLI{W   D  | } rd,rs1,   | shamt |

| Shift R  | tight Arithmetic | R | SRA   | rd,rs1,rs2   | SRA(W D)    | rd,rs1,     | rs2   |

| Shift R  | Right Arith Imm  | I | SRAI  | rd,rs1,shamt | SRAI (W D   | } rd,rs1,   | shamt |

| Arithme  | etic ADD         | R | ADD   | rd,rs1,rs2   | ADD{W   D}  | rd,rs1,     | rs2   |

|          | NDD Immediate    | I | ADDI  | rd,rs1,imm   | ADDI {W   D | } rd,rs1,:  | imm   |

|          | SUBtract         | R | SUB   | rd,rs1,rs2   | SUB{W D}    | rd,rs1,     | rs2   |

| Lo       | oad Upper Imm    | U | LUI   | rd,imm       | Opti        | onal Com    | pres  |

| Add Up   | per Imm to PC    | U | AUIPC | rd, imm      | Category    | / Name      | Fmt   |

| Logical  | XOR              | R | XOR   | rd,rs1,rs2   | Loads       | Load Word   | CL    |

| )        | OR Immediate     | I | XORI  | rd,rs1,imm   | Lo          | ad Word SP  | CI    |

|          | OR               | R | OR    | rd,rs1,rs2   | ι           | oad Double  | CL    |

|          | OR Immediate     | I | ORI   | rd,rs1,imm   | Load        | d Double SP | CI    |

|          | AND              | R | AND   | rd,rs1,rs2   |             | Load Quad   | CL    |

|          | AND Immediate    | I | ANDI  | rd,rs1,imm   | Lo          | ad Quad SP  | CI    |

|          |                  |   |       |              |             |             |       |

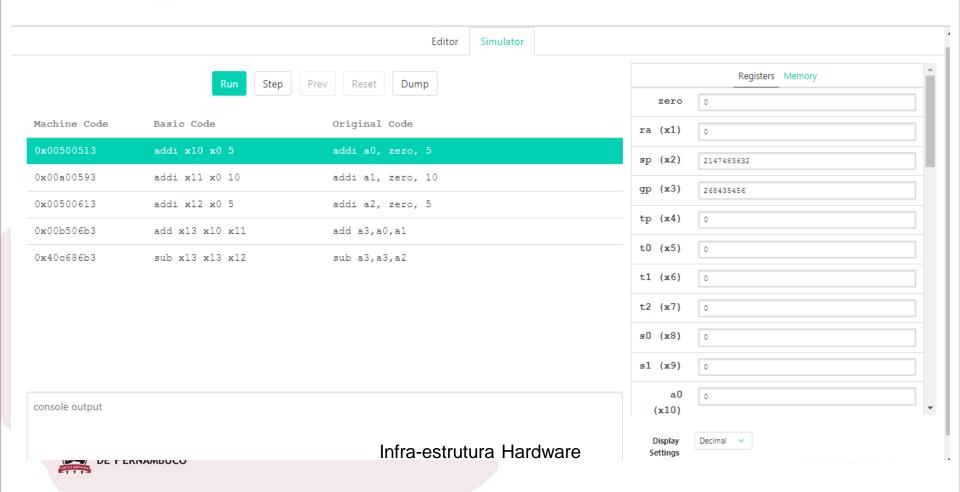

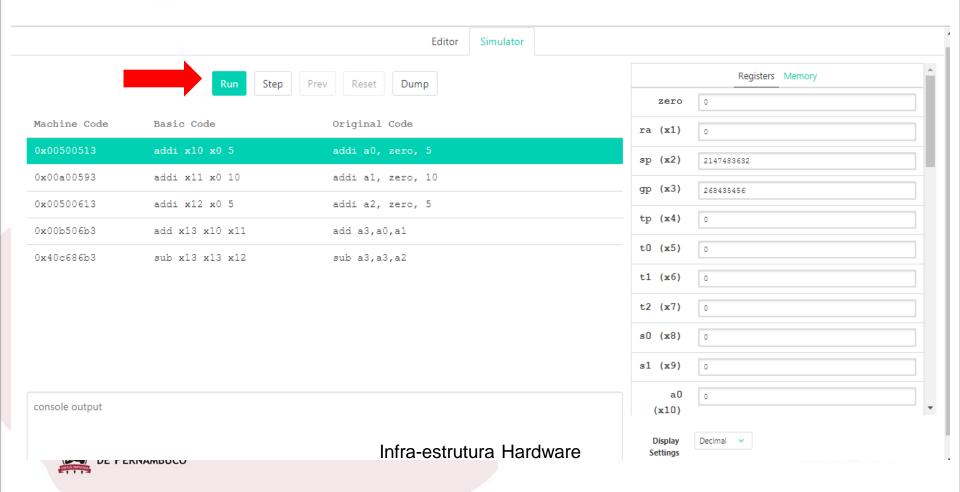

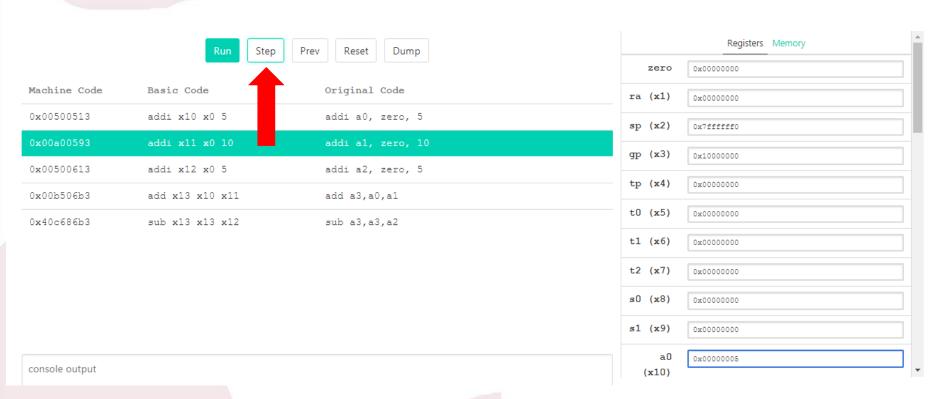

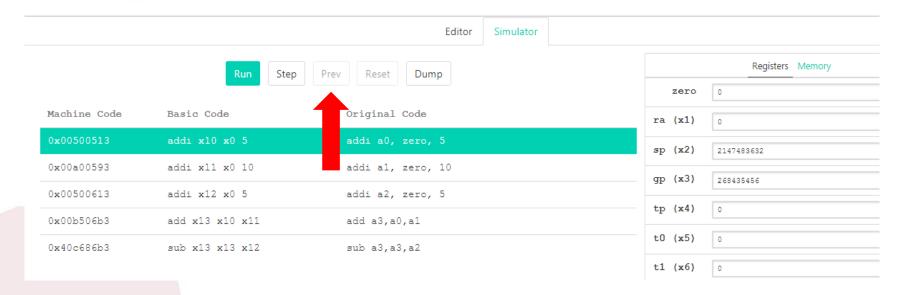

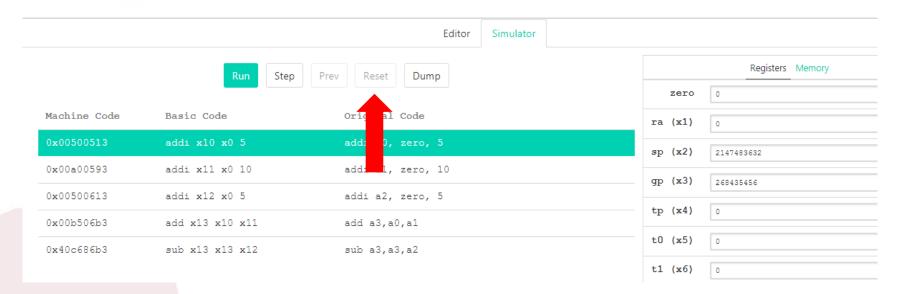

Escreva o seguinte código na aba Editor

```

addi a0, zero, 5

addi a1, zero, 10

addi a2, zero, 5

addi a3,a0,a1

sub a3,a3,a2

addi a2, zero, 5

addi a3,a0,a1

sub a3,a3,a2

```

Vá para aba Simulator para executar o código

- Original code seria o código em uma escrita com diretivas de alto nível. (ex: zero)

- Basic code seria o código com as diretivas traduzidas para assembly.

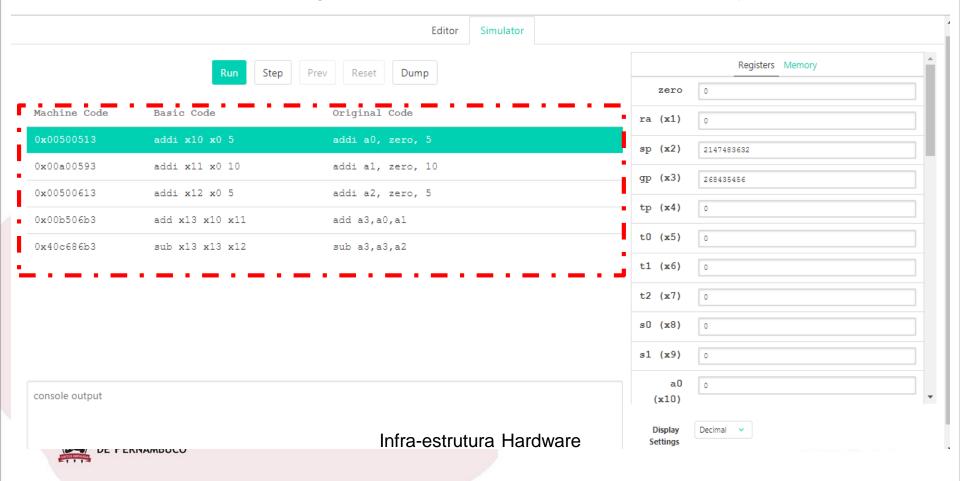

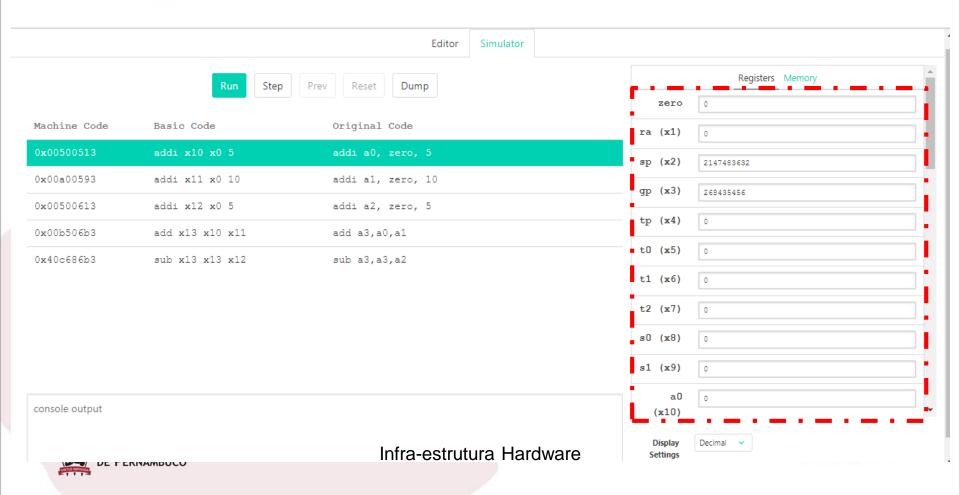

Visualize as informações armazenadas nos registradores do RISC V

Visualize as informações armazenadas nos registradores do RISC V

|    |               | Registers Memory | <u>^</u> |

|----|---------------|------------------|----------|

| :  | zero          | 0                |          |

| ra | (x1)          | 0                |          |

| sp | (x2)          | 2147483632       |          |

| gp | (x3)          | 268435456        |          |

| tp | (x4)          | 0                |          |

| t0 | (x5)          | 0                |          |

| t1 | ( <b>x</b> 6) | 0                |          |

| t2 | (x7)          | 0                |          |

| s0 | (x8)          | 0                |          |

Defina a base numérica em que valores serão visualizados

| s0 (x8)             | 0         |

|---------------------|-----------|

| s1 (x9)             | 0         |

| a0<br>(x10)         | 0         |

| Display<br>Settings | Decimal v |

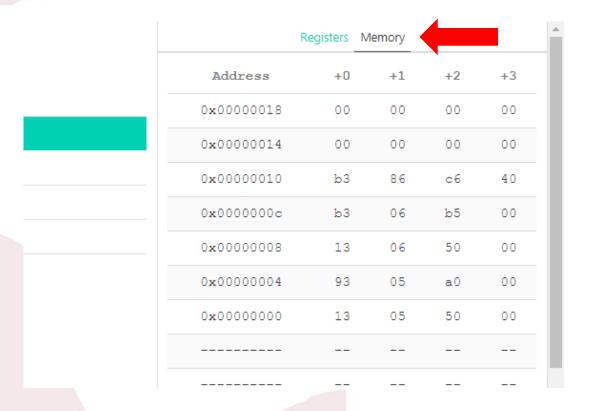

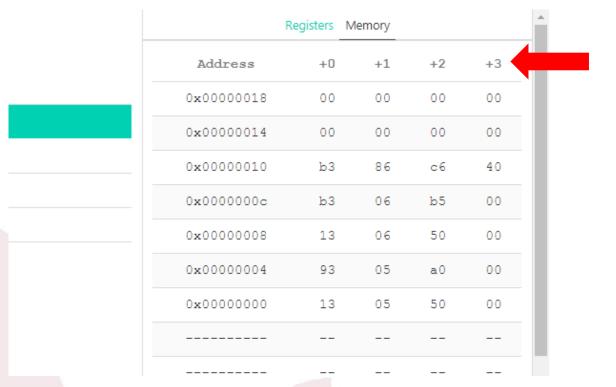

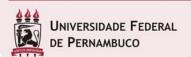

Visualize as informações armazenadas na memória do RISC V

Visualize as informações armazenadas na memória do RISC V

Deslocamento de Bytes

Vá direto para a região de memória específica

| 0x0ff               | 0                             | 0  | 0    |  |

|---------------------|-------------------------------|----|------|--|

| 0x0ff               | 0                             | 0  | 0    |  |

| Jump to             | . 🗸                           | Up | Down |  |

| Display<br>Settings | Text<br>Data<br>Heap<br>Stack |    |      |  |

O comando run executará todas as instruções sem parar

- Se alguma instrução tiver breakpoint o comando run parará nessa instrução

- Ao clicar na instrução você adicionará o breakpoint.

| Machine Code             | Basic Code                       | Original Code                 |

|--------------------------|----------------------------------|-------------------------------|

| 0x00500513               | addi x10 x0 5                    | addi a0, zero, 5              |

| 0x00a00593               | addi x11 x0 10                   | addi a1, zero, 10             |

|                          |                                  |                               |

| 0x00500613               | addi x12 x0 5                    | addi a2, zero, 5              |

| 0x00500613<br>0x00b506b3 | addi x12 x0 5<br>add x13 x10 x11 | addi a2, zero, 5 add a3,a0,a1 |

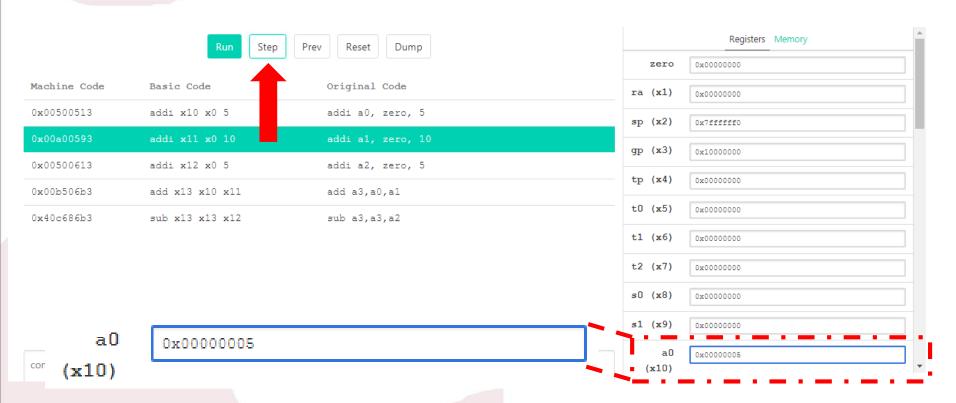

O comando step executa instrução por instrução

Valores dos registradores são atualizados de acordo com a instrução

É possível voltar cada passo

Ou voltar para o começo

#### Console output

#### Visualize os dados no console

|              | Run Ste        | Prev Reset Dump                |

|--------------|----------------|--------------------------------|

| Machine Code | Basic Code     | Original Code                  |

| 0x00100513   | addi x10 x0 1  | addi a0 x0 1 # print_int ecall |

| 0x02a00593   | addi x11 x0 42 | addi a1 x0 42 # integer 42     |

| 0x00000073   | ecall          | ecall                          |

42

#### Console output

- Para visualizar:

- Carregue a ID (1 para inteiro e 4 para string)

no registrador a0 e carregue o argumento em a1 – a7.

| ID ( a0 ) | Name            | Description                                                    |

|-----------|-----------------|----------------------------------------------------------------|

| 1         | print_int       | prints integer in a1                                           |

| 4         | print_string    | prints the null-terminated string whose address is in a1       |

| 9         | sbrk            | allocates a1 bytes on the heap, returns pointer to start in a0 |

| 10        | exit            | ends the program                                               |

| 11        | print_character | prints ASCII character in a1                                   |

| 17        | exit2           | ends the program with return code in a1                        |

#### Console output

- Para visualizar:

- Em seguida, chame a instrução ecall (environment call)

#### Console output

- Exemplo para testar:

- Escreva este código e em seguida clique em run

```

addi a0 x0 1 # print_int ecall

addi a1 x0 42 # integer 42

ecall

```

#### Console output

- Visualize os dados no console

- Deverá aparecer o valor 42 no console

42

#### Console output

- Para visualizar:

- Mas detalhes sobre environment call:

- https://github.com/kvakil/venus/wiki/Environmental-Calls

| ID ( a0 ) | Name            | Description                                                    |  |  |

|-----------|-----------------|----------------------------------------------------------------|--|--|

| 1         | print_int       | prints integer in a1                                           |  |  |

| 4         | print_string    | prints the null-terminated string whose address is in a1       |  |  |

| 9         | sbrk            | allocates a1 bytes on the heap, returns pointer to start in a0 |  |  |

| 10        | exit            | ends the program                                               |  |  |

| 11        | print_character | prints ASCII character in a1                                   |  |  |

| 17        | exit2           | ends the program with return code in a1                        |  |  |

Escreva o seguinte código no espaço Editor

.data

a: .word 4

.text

lw a1,a addi a0, zero, 0 loop:

addi a0,a0,1

bne a0,a1,loop

```

Editor Simulator

1 .data

2 a: .word 4

3 .text

4 lw a1,a

addi a0, zero, 0

loop:

addi a0,a0,1

bne a0,a1,loop

```

# Exemplo de Programa em Linguagem de Montagem

- Diretivas suportadas

- https://github.com/kvakil/venus/wiki/Assembler-Directives

| Directive | Effect                                                               |  |  |

|-----------|----------------------------------------------------------------------|--|--|

| .data     | Store subsequent items in the [[static segment                       |  |  |

| .text     | Store subsequent instructions in the [[text segment                  |  |  |

| .byte     | Store listed values as 8-bit bytes.                                  |  |  |

| .asciiz   | Store subsequent string in the data segment and add null-terminator. |  |  |

| .word     | Store listed values as unaligned 32-bit words.                       |  |  |

| .glob1    | Makes the given label global.                                        |  |  |

| .float    | Reserved.                                                            |  |  |

| .double   | Reserved.                                                            |  |  |

| .align    | Reserved.                                                            |  |  |

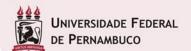

A memória de dados começa no endereço 0x10000000 Que é o mesmo apontado pelo registrador gp

Instrução lw a1,a terminou registrador x11 (ou a1) agora está com o valor 4 a0 0x00000000 (x10)a1 0x00000004 (x11)a2 0x00000000

(x12)

Após executar o run o registrador x10 (ou a0) passou a ter o valor 4

```

a0 0x00000004 (x10)

a1 0x00000004 (x11)

```

- Para declarar uma string:

- Nome: .asciiz "meu nome é.."

- Exemplo:

- msg:.asciiz"1-2-3-4-5"

- lb x5, 0(gp) #colocando o valor que esta na memoria

#### Escrevam o seguinte código:

- .data

- msg:.asciiz "1-2-3-4-5"

- text

- lb a2,(0)gp

- lb a3,(1)gp

- lb a4,(2)gp

- lb a5,(3)gp

- lb a6,(4)gp

- lb a7,(5)gp

Observe que o registrador gp aponta para o início da string na memória

Execute run e verifique os valores da string nos registradores

| a2<br>(x12) | '1' |

|-------------|-----|

| a3<br>(x13) | '-' |

| a4<br>(x14) | '2' |

| a5<br>(x15) | '-' |

| a6<br>(x16) | '3' |

| a7<br>(x17) | '-' |

#### Outra maneira similar

- data

- msg:.asciiz "1-2-3-4-5"

- .text

- la a1, msg

- lb a2,(0)a1

- lb a3,(1)a1

- lb a4,(2)a1

- lb a5,(3)a1

- lb a6,(4)a1

A instrução la Carrega o endereço base de msg

- É possível inicializar dados na memória usando diretivas como as presentes <u>aqui</u>

- Por exemplo, para declarar uma variável inteira a:

- a: .word *valor*

- String nome:

- Nome: .string "meu nome é.."

- Nome: .asciz "meu nome é.."

Por exemplo, para declarar uma variável inteira a:

- a: .word *valor*

Exemplo: a: .word 10

b: .word 20

- Para declarar uma string:

- Nome: .string "meu nome é.."

- Nome: .asciz "meu nome é.."

- Exemplo:

- msg:.string "1-2-3-4-5"

- Ib x5, 0(gp) #colocando o valor que esta na memoria

#### Escrevam o seguinte código:

- .data

- msg:.string "1-2-3-4-5"

- text

- lb a2,(0)gp

- lb a3,(1)gp

- lb a4,(2)gp

- lb a5,(3)gp

- lb a6,(4)gp

- lb a7,(5)gp

| Directive | Arguments | Description                                      | .dtpreldword |            | 64-bit thread local word                              |

|-----------|-----------|--------------------------------------------------|--------------|------------|-------------------------------------------------------|

| .2byte    |           | 16-bit comma separated words (unaligned)         | .dtprelword  |            | 32-bit thread local word                              |

| .4byte    |           | 32-bit comma separated words (unaligned)         | .sleb128     | expression | signed little endian base 128, DWARF                  |

| .8byte    |           | 64-bit comma separated words (unaligned)         | .uleb128     | expression | unsigned little endian base 128, DWARF                |

| .half     |           | 16-bit comma separated words (naturally aligned) | .asciz       | "string"   | emit string (alias for .string)                       |

| .word     |           | 32-bit comma separated words (naturally aligned) | .string      | "string"   | emit string                                           |

| .dword    |           | 64-bit comma separated words (naturally aligned) | .incbin      | "filename" | emit the included file as a binary sequence of octets |

| .byte     |           | 8-bit comma separated words                      | .zero        | integer    | zero bytes                                            |

#### Atividade Prática

- Responder questões 1, 2 e 3 da lista disponível no site até às 23:59 de hoje (23/08).

- Questões 4 6 até o dia (03/09) às 23:59.