# Arquitetura de Sistemas Embarcados

Edna Barros (ensb@cin.ufpe.br)

Centro de Informática – UFPE

Capítulo 3 Processadores de Propósito Geral:

Software

## Introdução

- Processadores de Propósito Geral

- Processador projetado para uma variedade de tarefas computacionais

- Baixo custo unitário (Custo NRE para grande volume)

- Motorola vendeu meio bilhão de microcontroladores 68HC05 em 1996

- Cuidadosamente projetado

- · Otimiza desempenho, tamanho e potência

- Reduzido time-to-market (protótipo), grande flexibilidade

- · Usuário apenas descreve o software

- "microprocessor" "micro" usado devido a ser implementado com poucos circuitos

Centro de Informática Arquitetura de Sistemas Embarcados 3

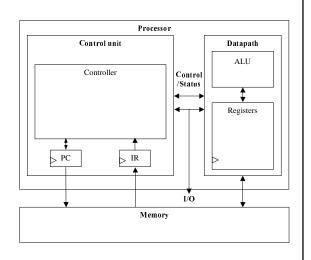

# Arquitetura Básica

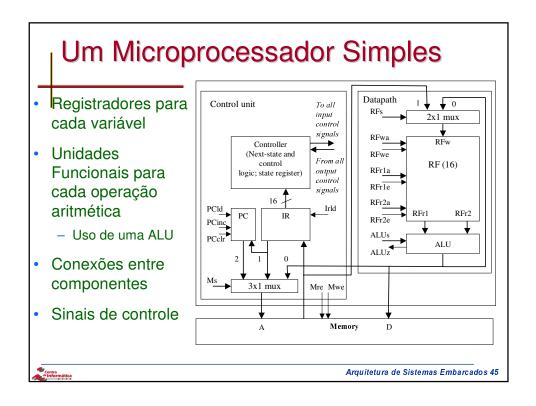

- Unidade de Controle e de Processamento

- Diferenças

- Unidade de Processamento é genérica

- Unidade de controle não armazena algoritmo (memória)

Centro de Informática

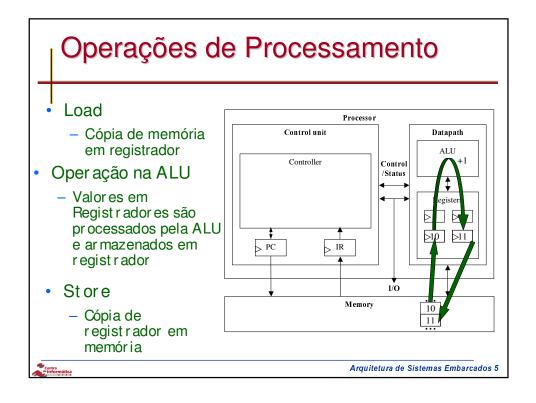

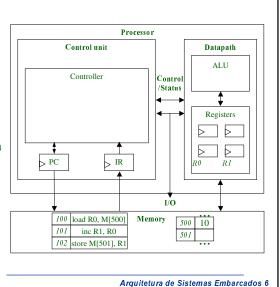

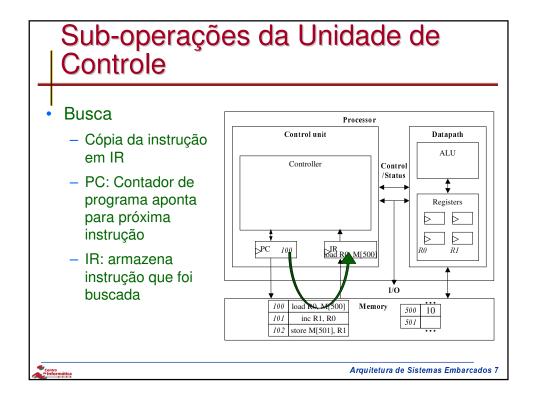

#### Unidade de Controle

- Unidade de Controle: configura operações do datapath

- Sequência de operações (instruções) desejadas armazenadas na memória (programa)

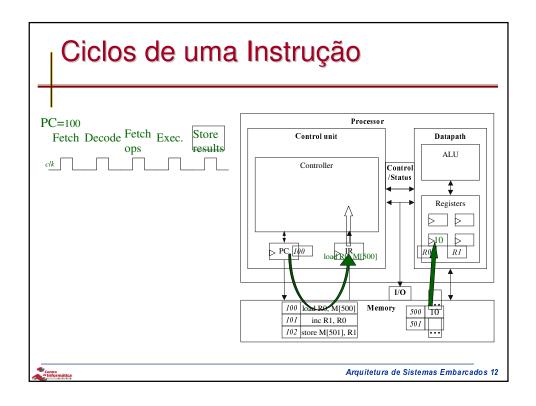

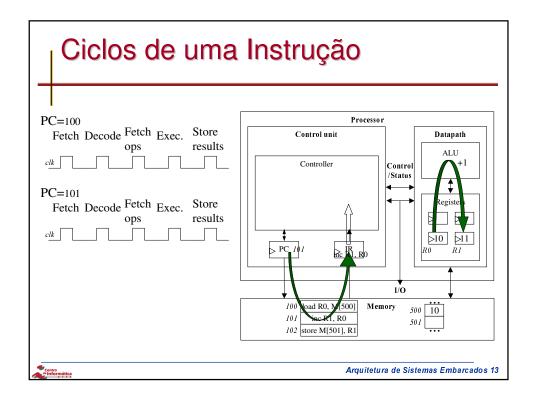

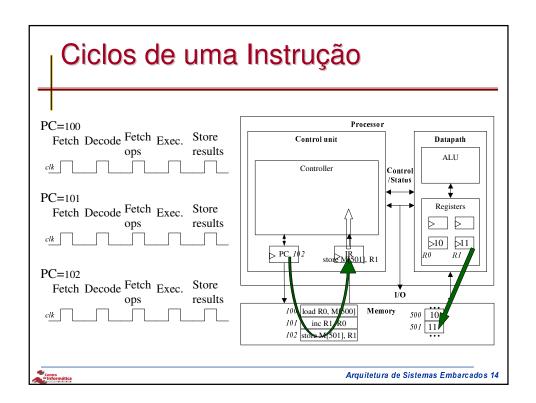

- Ciclo de Instrução várias suboperações (cada uma em um ciclo de relógio)

- Busca: armazena instrução em IR, atualiza PC

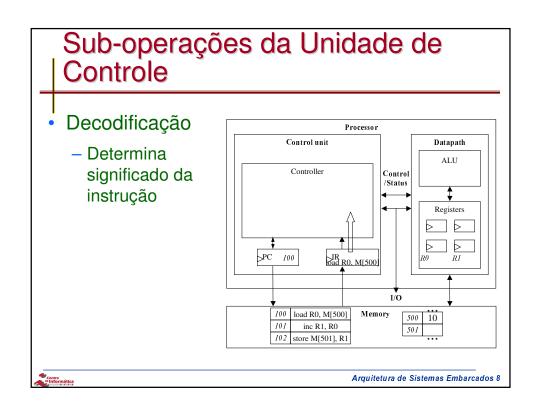

- Decodificação: determina o que a instrução significa

- Busca de Operandos: cópia de dados da memória para registradores na unid.

Processamento

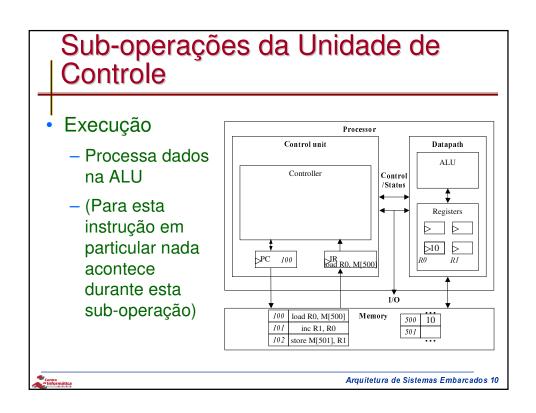

- Execução: Processa dados na

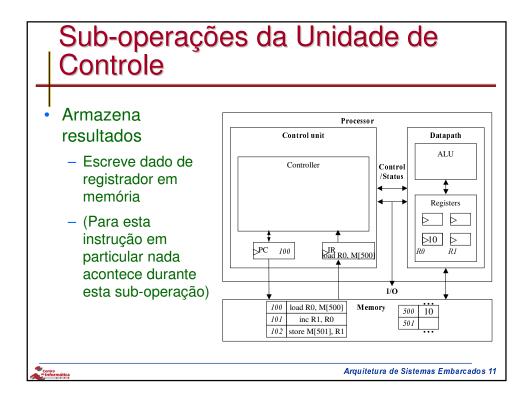

- Armazena resultados: escreve resultados de registrador na memória

#### Sub-operações da Unidade de Controle Busca de Processor Control unit Datapath **Operandos** Controller - Cópia de dados /Status da memória Registers para registradores no >10 IR oad R0, M[500 PС 100 datapath Memory 100 load R0, M[500] 500 10 inc R1, R0 50 I 102 store M[501], R1 Arquitetura de Sistemas Embarcados 9

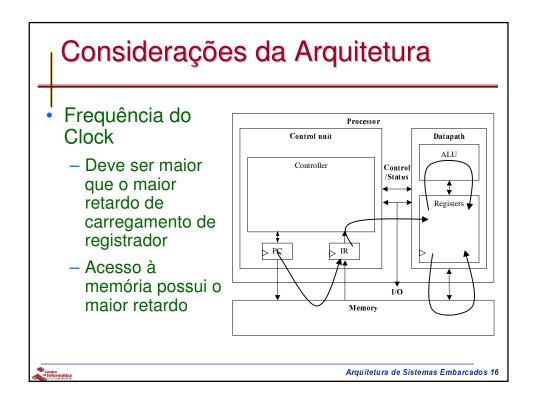

#### Considerações da Arquitetura Processador de N-bits Processor ALU, registradores, Control unit Datapath barramento, interface Controller de memória N-bits Control /Status Comum em aplic. emb: Registers 8-bit, 16-bit, 32-bit Comum em Desktop/servidores: > PC | IR 32-bit, ou 64 Tamanho do PC determina espaço de Memory endereçamento Arquitetura de Sistemas Embarcados 15

# Arquiteturas Superescalares e VLIW

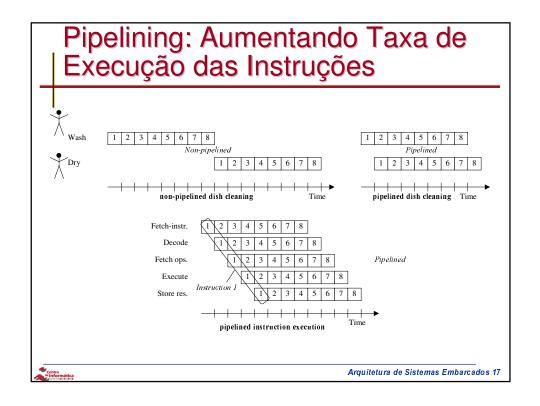

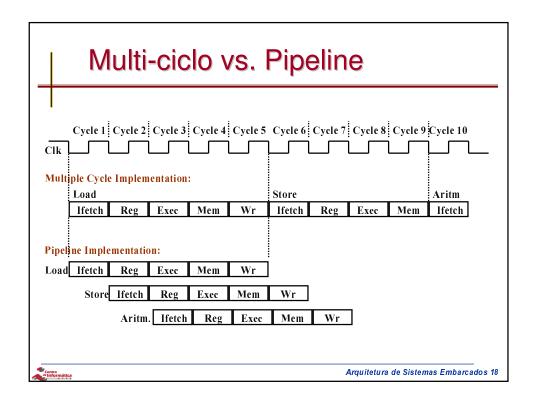

- Desempenho pode ser melhorado por:

- Clock mais rápido

- Pipelining

- Múltiplas ALUs permitindo a execução de uma de uma sequência de instruções

- Superescalares

- Escalar: operações não vetoriais

- Instruções buscadas em blocos e se executa o maior número possível

- » Hardware adicional para descobrir instruções independentes

- VLIW

- cada palavra na memória tem múltiplas instruções independentes

- » Compilador deve descobrir e escalonar instruções

- » Aumento de popularidade

Centro de Informática

## Visão do Programador

- Programador não necessita visão detalhada da implementação

- Precisa saber quais instruções podem ser executadas

- Dois Níveis de Abstração

- Linguagem de Montagem (Assembly level)

- Linguagens Estruturadas (C, C++, Java, etc.)

- Projetos são feitos usando linguagens estruturadas

- MAS algum nível de assembly PODE ser necessário

- Drivers: parte do programa que se comunica com e/ou controla outro dispositivo

- Com considerações detalhadas de tempo e manipulação de bits

- · Nível de assembly pode ser o ideal

Centro de Informática

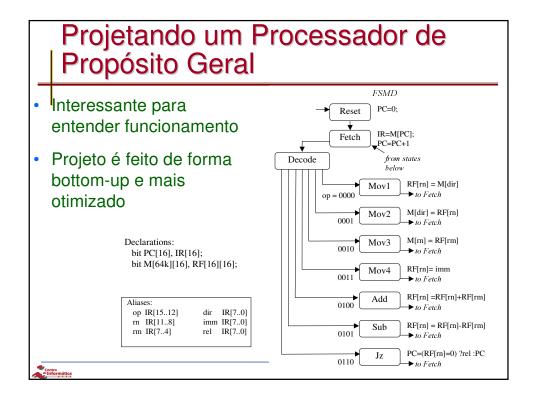

# Instruções Nível Assembly

Instruction 1 opcode operand1 operand2

Instruction 2 opcode operand1 operand2

Instruction 3 opcode operand1 operand2

Instruction 4 opcode operand1 operand2

...

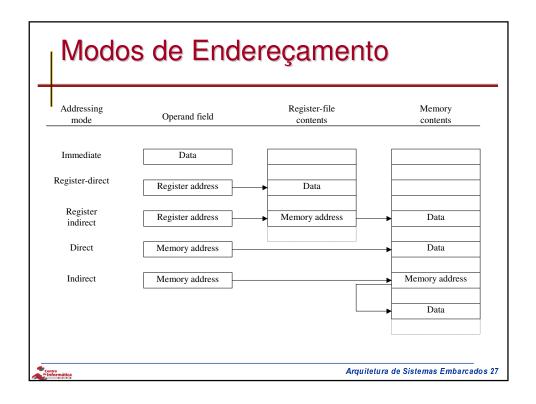

- Repertório de Instruções:

- Define o conjunto de instruções que o processador pode executar

- Transferência de Dado: memória/registrador, registrador/registrador, I/O, etc.

- Aritméticas e Lógicas

- Desvios: determina outro valor para PC (diferente de PC+1)

Centro Informática Arquitetura de Sistemas Embarcados 25

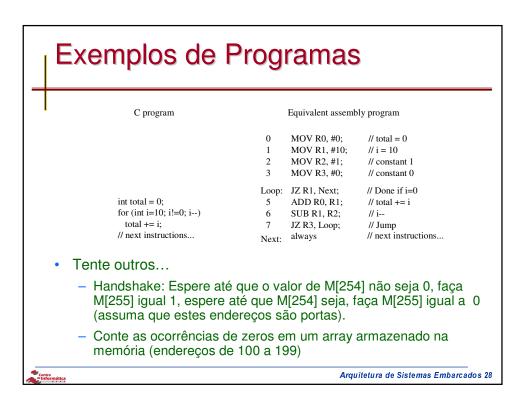

#### Um Repertório de Instruções Simples Assembly instruct. First byte Second byte Operation MOV Rn, direct 0000 Rn direct Rn = M(direct)MOV direct, Rn 0001 Rn direct M(direct) = RnMOV @Rn, Rm 0010 Rn RmM(Rn) = RmMOV Rn, #immed. 0011 Rn immediate Rn = immediateADD Rn, Rm 0100 Rn RmRn = Rn + RmSUB Rn, Rm 0101 Rn = Rn - RmRn Rm JZ Rn, relative 0110 PC = PC + relativerelative (only if Rn is 0) opcode operands Arquitetura de Sistemas Embarcados 26

## Visão do Programador

- Espaço de Programa e de Dados

- Processadores embarcados são bastantes limitados (em geral)

- e.g., 64 Kbytes de programa, 256 bytes de RAM (expansível)

- Registradores: Quantos existem?

- Somente para programadores em assembly

- I/O

- Como se comunicar com sinais externos?

- Interrupções

Centro de Informática Arquitetura de Sistemas Embarcados 29

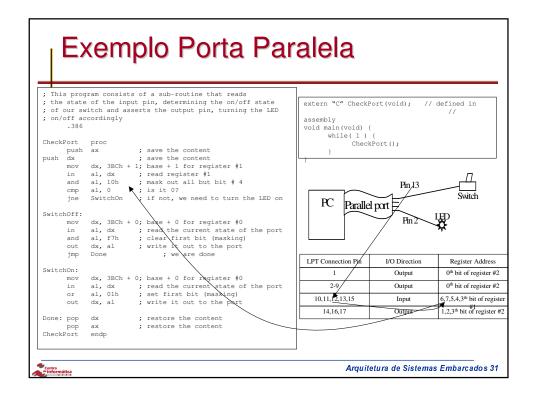

## Exemplo: driver de porta paralela

| LPT Connection Pin | I/O Direction | Register Address                   |                      |

|--------------------|---------------|------------------------------------|----------------------|

| 1                  | Output        | 0 <sup>th</sup> bit of register #2 |                      |

| 2-9                | Output        | 0th bit of register #2             | _                    |

| 10,11,12,13,15     | Input         | 6,7,5,4,3th bit of register #1     | Pin 13               |

| 14,16,17           | Output        | 1,2,3th bit of register #2         | Parallel port Switch |

|                    |               |                                    | Pin2 LIFD            |

|                    |               |                                    |                      |

- Usando linguagem assembly pode-se configurar a porta paralela de um PC para se fazer E/S digital

- Escrita e leitura de 3 registradores especiais (conforme tabela que mostra pinos do conector da porta e sua posição nos registradores

- Exemplo: porta paralela monitora uma chave e acende ou apaga um LED de acordo com a posição da chave

Centro de Informática

# Sistema Operacional

- Software opcional que fornece serviços de "baixo nível" para a aplicação

- Gerenciamento de arquivos e acesso a disco

- Interface entre teclado e vídeo

- Escalonamento de múltiplos programas para execução

- Ou mesmo múltiplas threads de um programa

- Programa faz chamadas ao S.O.

```

DB file_name "out.txt" -- store file name

MOV R0, 1324 -- system call "open" id

MOV R1, file_name -- address of file-name

INT 34 -- cause a system call

JZ R0, L1 -- if zero -> error

. . . read the file

JMP L2 -- bypass error cond.

L1:

. . . handle the error

L2:

```

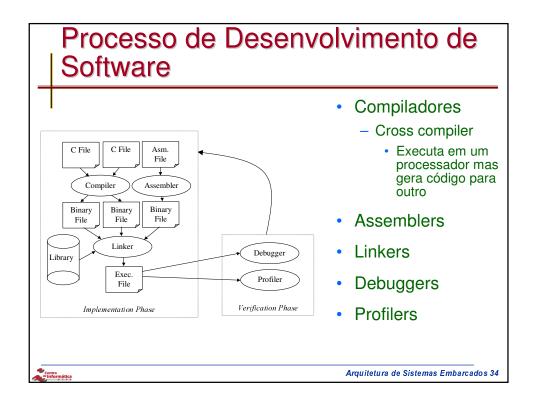

#### Ambiente de Desenvolvimento

- Processador de Desenvolvimento

- Processador usado na escrita e depuração de programas

- Usualmente PC

- Processador Target

- Processador que irá executar o programa no sistema embarcado

- · Usualmente diferentes do processador de desenvolvimento

Centro de Informática

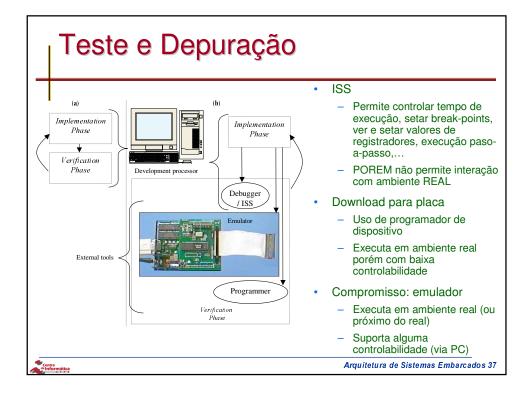

#### Executando um programa

- Se processador de desenvolvimento é diferente do processador alvo, como executar o código compilado???

- Duas opções:

- Download para processador alvo

- Simulação

- Simulação

- Um método: Descrever o processador usando HDL (Hardware description language)

- Lento

- Outro Método: Usar ISS (Instruction set simulator)

- Executa no processador de desenvolvimento as instruções do processador alvo

# Instruction Set Simulator para o Processador Simples

```

#include <stdio.h>

typedef struct {

unsigned char first_byte, second_byte;

} instruction;

instruction program[1024]; //instruction memory

unsigned char memory[256]; //data memory

void run_program(int num_bytes) {

int pc = -1;

unsigned char reg[16], fb, sb;

while(++pc < (num_bytes / 2)) {

fb = program[pc].first_byte;

sb = program[pc].second_byte;

switch (fb >> 4) {

case 0: reg[fb & 0x0f] = memory[sb]; break;

case 1: memory[sb] = reg[fb & 0x0f] = reg[sb >> 4]; break;

case 4: reg[fb & 0x0f] == reg[sb >> 4]; break;

case 6: reg[fb & 0x0f] == reg[sb >> 4]; break;

case 6: reg[fb & 0x0f] == reg[sb >> 4]; break;

case 6: reg[fb & 0x0f] == reg[sb >> 4]; break;

case 6: reg[fb & 0x0f] == reg[sb >> 4]; break;

case 6: reg[fb & 0x0f] == reg[sb >> 4]; break;

case 6: reg[fb & 0x0f] == reg[sb >> 4]; break;

case 6: reg[fb & 0x0f] == reg[sb >> 4]; break;

case 6: reg[fb & 0x0f] == reg[sb >> 4]; break;

case 6: reg[fb & 0x0f] == reg[sb >> 4]; break;

case 6: reg[fb & 0x0f] == reg[sb >> 4]; break;

case 6: reg[fb & 0x0f] == reg[sb >> 4]; break;

case 6: reg[fb & 0x0f] == reg[sb >> 4]; break;

case 6: reg[fb & 0x0f] == reg[sb >> 4]; break;

case 6: reg[fb & 0x0f] == reg[sb >> 4]; break;

case 6: reg[fb & 0x0f] == reg[sb >> 4]; break;

case 6: reg[fb & 0x0f] == reg[sb >> 4]; break;

case 6: reg[fb & 0x0f] == reg[sb >> 4]; break;

case 6: reg[fb & 0x0f] == reg[sb >> 4]; break;

case 6: reg[fb & 0x0f] == reg[sb >> 4]; break;

case 6: reg[fb & 0x0f] == reg[sb >> 4]; break;

case 6: reg[fb & 0x0f] == reg[sb >> 4]; break;

case 6: reg[fb & 0x0f] == reg[sb >> 4]; break;

case 6: reg[fb & 0x0f] == reg[sb >> 4]; break;

case 6: reg[fb & 0x0f] == reg[sb >> 4]; break;

case 6: reg[fb & 0

```

Centro de Informátic

#### Processadores de Repertório de Instruções de Aplicação Específica (ASIPs)

- · Processadores de propósito geral

- Algumas vezes MUITO GENÉRICOS para ser eficiente para aplicação específica

- Ex: processamento de vídeo: buffers e operações em arrays

- MAS processador de aplicação única possui alto custo NRE e não é programável

- ASIPs Aplicam-se a um domínio particular

- Possuem características de arquitetura específicas ao domínio

- Ex: controle embarcado, processamento digital de sinais, processamento de vídeo, processamento de rede, telecomunicações, etc.

- Suportam uma área de aplicação

- São Programáveis

Centro de Informática

## Exemplo de ASIP : Microcontrolador

- Para aplicações de controle

- Leitura de sensores, ativar atuadores

- Manipula com eventos: existe dados mas em pequena quantidade

- Ex: disk drive, máguina de lavar, forno de microondas, etc...

- Características dos Microcontroladores

- Periféricos em Único CHIP

- Temporizadores, conversores analógico-digital, comunicação serial, etc...

- · Acesso através de registradores (facilidade de programação)

- Programa de memória e dados no chip

- Acesso a vários dos pinos do chip

- Instruções para manipulação de bits e operações de baixo-nível

Centro de Informática Arquitetura de Sistemas Embarcados 39

# Exemplo de ASIP: Digital Signal Processors (DSP)

- Para aplicações de processamento de sinais

- Grande quantidade de dado digitalizado (em streaming)

- Transformações nos dados devem ser rápidas

- Ex: filtro para telefone celular, TV digital, sintetizador de música

- Características dos DSPs

- Várias unidades de execução

- Instrução Multiplica-acumula

- Operações eficientes em vetores, ex: add dois arrays

- ALUs vetoriais, loop buffers, etc...

Centro de Informática

#### ASIPs customizados

Processadores adquiridos como módulo de propriedade intelectual (IP)

- Modelo VHDL sintetizável

- Layout

- Possibilidade de ajustar hardware (adicionar ou retirar instruções)

- Grande impacto no desempenho, tamanho e potência

- Problema: necessidade de compilador/depurador para ASIP customizado

- · Uma solução: geração automática de compiladores/depuradores

- e.g., www.tensillica.com

- Outra solução: retargettable compilers

- e.g., <u>www.improvsys.com</u> (customized VLIW architectures)

Arquitetura de Sistemas Embarcados 41

## Selecionando o microprocessador

- Características

- Técnicas: velocidade, potência, tamanho, custo

- Outras: ambiente de desenvolvimento, conhecimento prévio, licenças, ...

- Como avaliar o desempenho de um processador?

- Velocidade do Clock: nr. de instruções por ciclo pode diferir

- Instruções por segundo: tipo de instruções podem diferir

- Dhrystone: Benchmark Sintético, desenvolvido em 1984. Dhrystones/sec.

- MIPS: 1 MIPS = 1757 Dhrystones per second (based on Digital's VAX 11/780).

- 750 MIPS = 750\*1757 = 1,317,750 Dhrystones per second

- SPEC: conjunto de benchmarks mais realísticos orientados a desktop

- EEMBC EDN Embedded Benchmark Consortium, www.eembc.org

- Benchmarks: automóveis, eletrônica de consumo, redes, automação de escritório, telecomunicações.

Centro de Informática

| Processor              | Clock speed | Periph.                                          | Bus Widtl    |               | Power | Trans. | Price |

|------------------------|-------------|--------------------------------------------------|--------------|---------------|-------|--------|-------|

| Intel PIII             | 1GHz        | 2x16 K<br>L1, 256K<br>L2, MMX                    | 32           | ~900          | 97W   | ~7M    | \$900 |

| IBM<br>PowerPC<br>750X | 550 MHz     | 2x32 K<br>L1, 256K<br>L2                         | 32/64        | ~1300         | 5W    | ~7M    | \$900 |

| MIPS<br>R5000          | 250 MHz     | 2x32 K<br>2 way set assoc.                       | 32/64        | NA            | NA    | 3.6M   | NA    |

| StrongARM<br>SA-110    | 233 MHz     | None                                             | 32           | 268           | 1W    | 2.1M   | NA    |

|                        |             |                                                  | Microco      | ontroller     |       |        |       |

| Intel<br>8051          | 12 MHz      | 4K ROM, 128 RAM,<br>32 I/O, Timer, UART          | 8            | ~1            | ~0.2W | ~10K   | \$7   |

| Motorola<br>68HC811    | 3 MHz       | 4K ROM, 192 RAM,<br>32 I/O, Timer, WDT,<br>SPI   | 8            | ~.5           | ~0.1W | ~10K   | \$5   |

|                        |             |                                                  | Digital Sign | al Processors |       |        |       |

| TI C5416               | 160 MHz     | 128K, SRAM, 3 T1<br>Ports, DMA, 13<br>ADC, 9 DAC | 16/32        | ~600          | NA    | NA     | \$34  |

| Lucent<br>DSP32C       | 80 MHz      | 16K Inst., 2K Data,<br>Serial Ports, DMA         | 32           | 40            | NA    | NA     | \$75  |

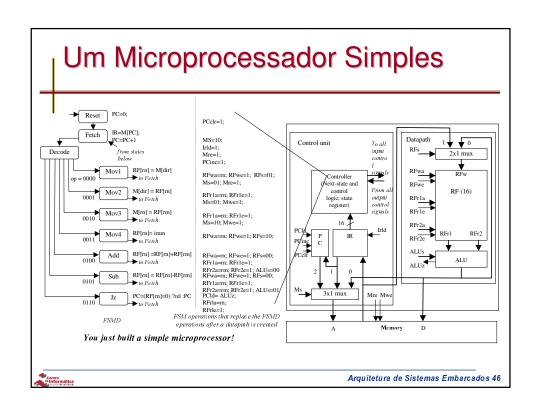

#### Resumo

- Processadores de Propósito Geral

- Bom desempenho, baixo custo NRE, flexível

- Controle, processamento e memória

- Uso de linguagens estruturadas

- Várias ferramentas disponíveis

- Simulador ISS e emuladores

- ASIPs

- Microcontroladores, DSPs, processadores de rede, ASIPs customizados

- · Escolha do processador é uma etapa importante

- Projetar um processador de propósito geral é conceitualmente o mesmo que projetar um processador de propósito específico

Centro de Informática