# Prototipação de Sistemas Digitais

Metodologia de Projetos Cristiano Araújo

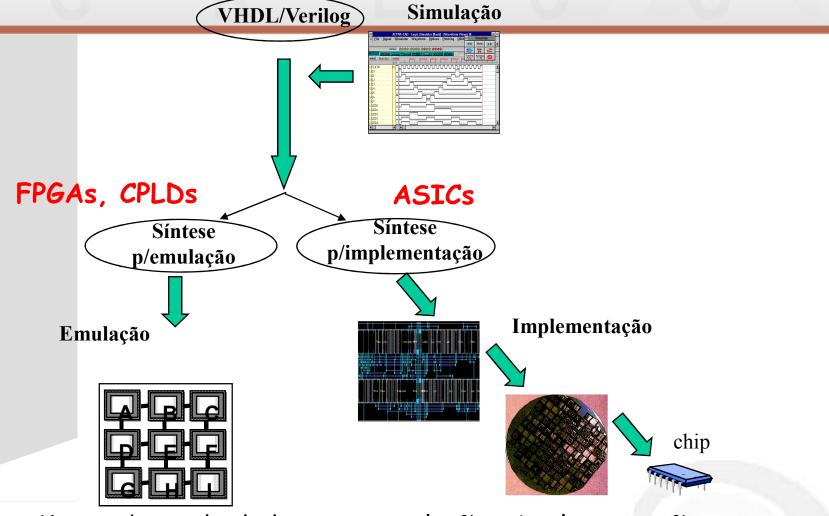

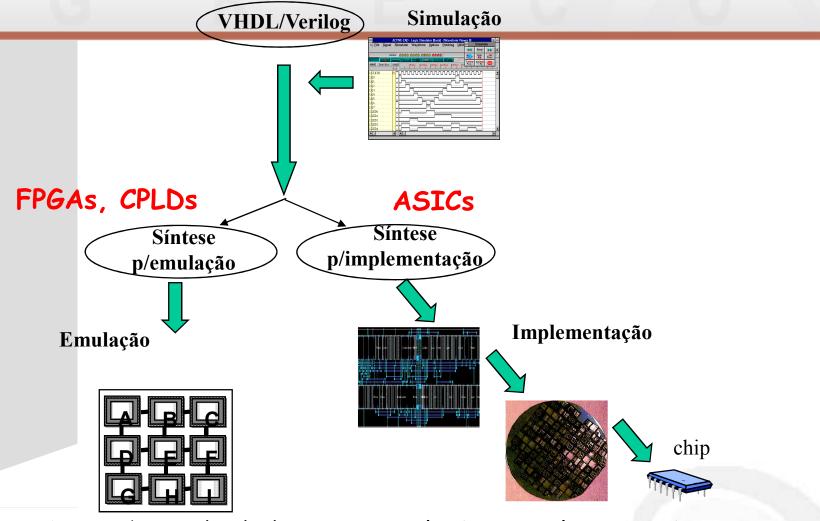

# Fluxo de projeto Emulação/Implementação do componente de harwdare

• Mesma base de dados para emulação e implementação 2007.estes durante a pæmulação seriamimais próximos possíveis da implementação final do projeto tação € CID / UFPE

# Comunicação: Cliente x projetista

### Vendedor

- Janela de mercado

- preço, etc.

### **Projetista**

- Ferramentas de CAD

- Engenharia concorrente

- Tecnologia

- Silicon foundry

- Aplicação

2008.1

Prototipação de Sistemas Digitais

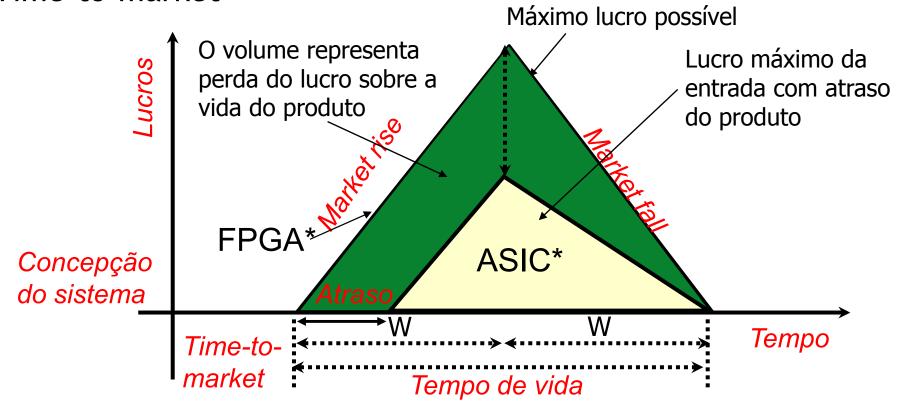

#### Time-to-market

- ☐ Em um mercado competitivo, qualquer atraso incorpora perda da parte deste mercado:

- Perda da janela de mercado

- Atraso para lançamento em função do longo ciclo de desenvolvimento

- O efeito da perda em lucro devido o atraso no lançamento do produto é maior que aquele custo de desenvolvimento

#### Time-to-market

O percentual de perda de lucro, do lucro possível, é dado pela área do maior retângulo menos a área do menor retângulo.

# O que é Metodologia de Projeto?

São sequências de transformações que partem de uma descrição e/ou especificação inicial de um sistema digital para se chegar a uma descrição final, válida para o processo de fabricação deste sistema, no menor espaço de tempo possível.

Metodologia

Conjunto de regras

**Procedimentos**

# Metodologia de projetos

#### Conjunto de regras

- Seqüência de Etapas

- Forma de Apresentação dos Resultados

- Linguagem Utilizada

#### **Procedimentos**

- Especificação

- Projeto de alto nível

- Implementação

- Teste

#### Gerência

- Organização

- Integridade de Dados

- Atribuições de Atividades

- Cronograma

- Controle de Qualidade

### Comportamental

# Níveis de abstração

### Transf. Registro

#### **Estrutural**

#### Layout Físico

# Níveis de abstração para descrição de um projeto

#### ☐ Descrição Comportamental

O sistema é descrito de forma comportamental, ou seja o modelamento comportamental que aponta algoritmicamente a funcionalidade requerida sem referenciar a estrutura do modelo.

#### Descrição RTL ou Data Flow

■ Nível de abstração seguinte abaixo da descrição comportamental. É caracterizado pela definição de um sistema em termos de registradores, chaves e unidades funcionais. Uma descrição RTL define uma arquitetura e incorpora a noção de relógio.

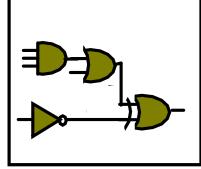

#### Descrição estrutural (Lógico)

Este nível é o mais baixo nível não físico para representação de um projeto. As descrições mostram a implementação lógica da função descrevendo a arquitetura para implementar o algoritmo comportamental.

#### Descrição Física

Neste nível é definida a geometria de implementação do circuito. Este nível depende da tecnologia.

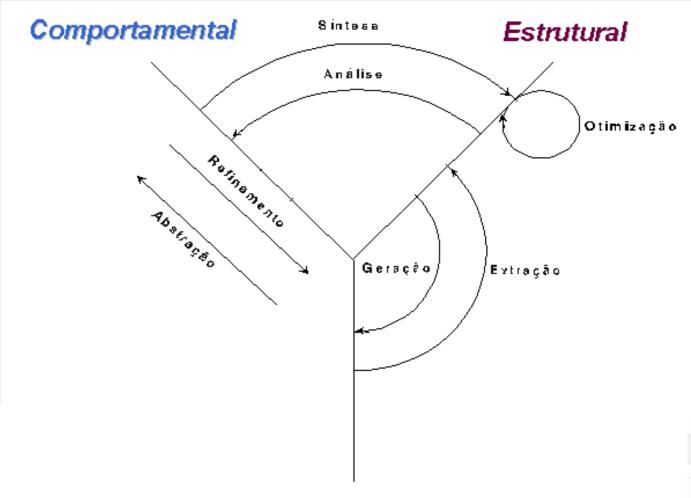

# Níveis de descrição de sistemas eletrônicos Diagrama de Gajski

#### Domínios

- Comportamental

- □ O comportamento do sistema é especificado, idealmente sem qualquer referência ao caminho que este comportamento vai ser implementado.

- Estrutural

- □ Trata o sistema como como uma hierarquia de elementos funcionais e suas interconexões.

- Físico

- □ A estrutura do projeto é mapeada no espaço, sem qualquer referência a funcionalidade do circuito.

# Diagrama de Gajski (Y)

Sistema **Comportamental** Estrutural algoritmo arquitetura CPU, memória Sistema proc., sub-sistema **Algoritmo** lógica ULA e registradores portas lógicas e FF circuito Equação booleana Equação Diferencial transistores Grupo de retang./políg. Células Macrocélulas Blocos/Chip Chip/board 2008.1 Prototipação de Sistemas Digitais 12

# Diagrama de Gajski

(Transição no diagrama Y definindo passos do projeto)

Físico/geométrico

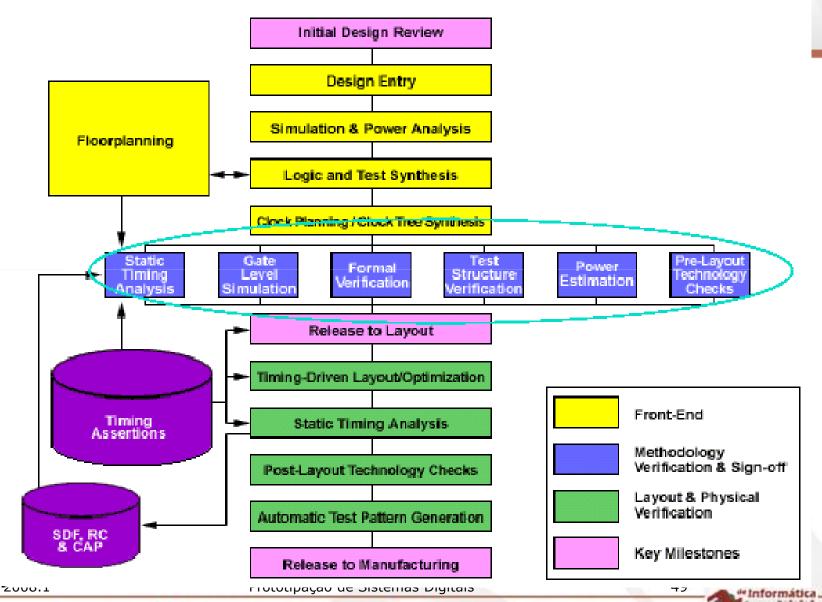

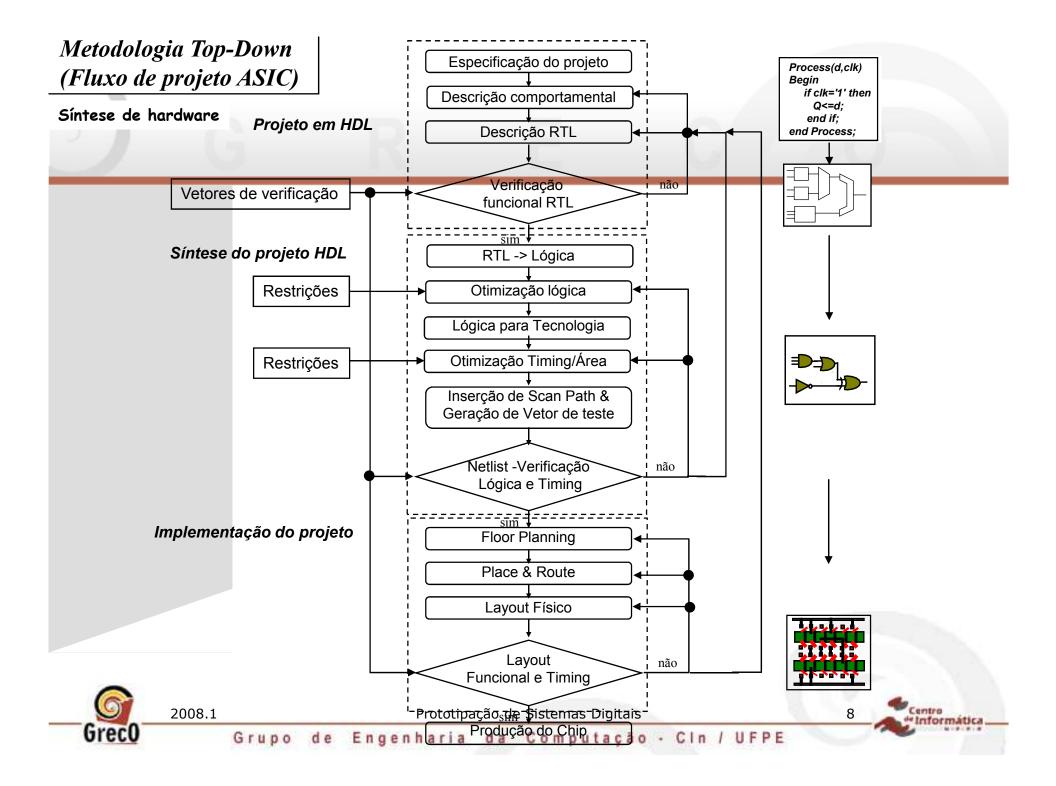

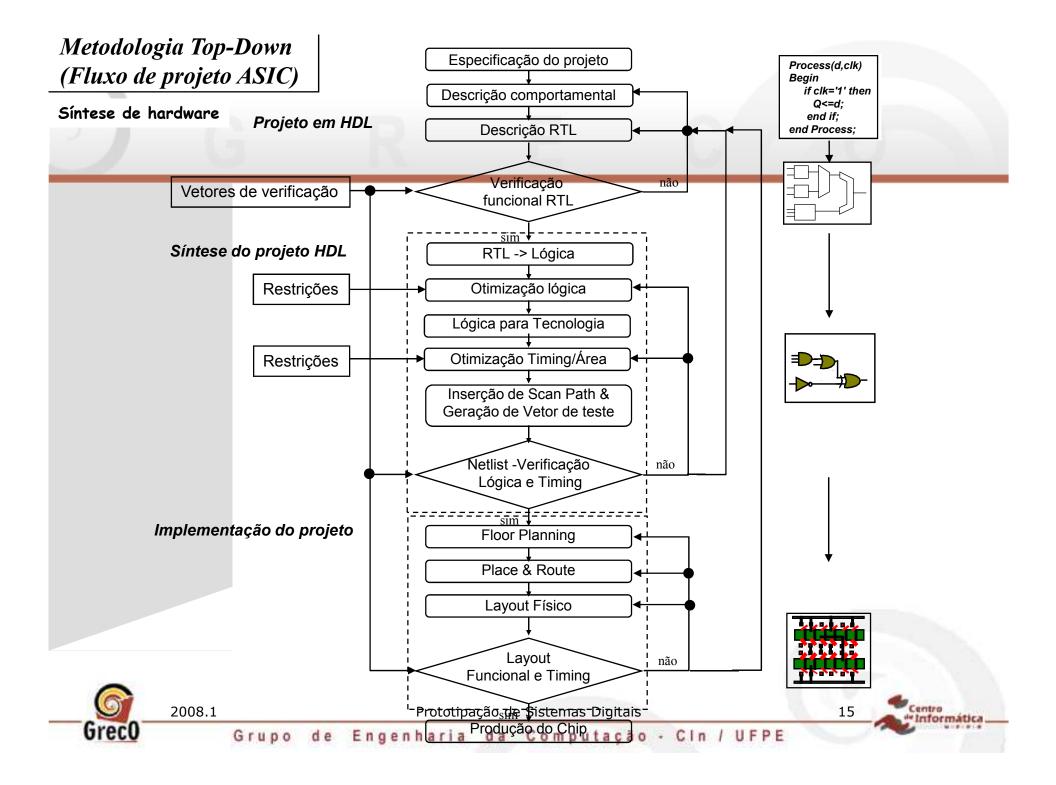

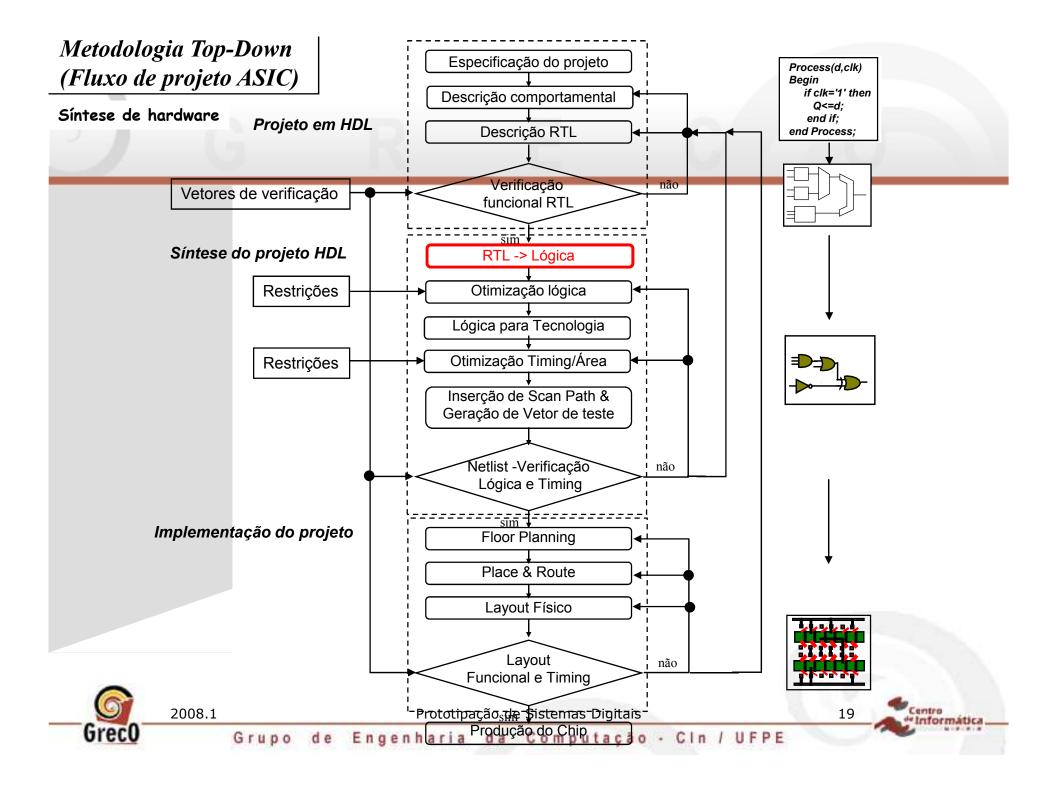

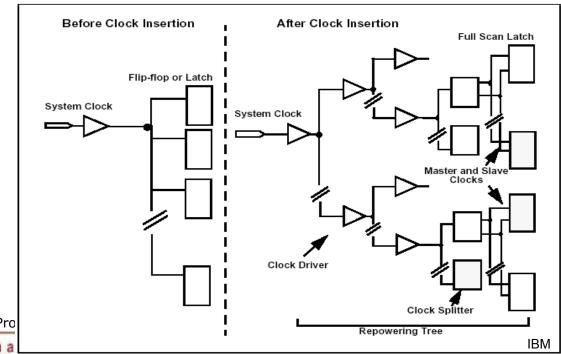

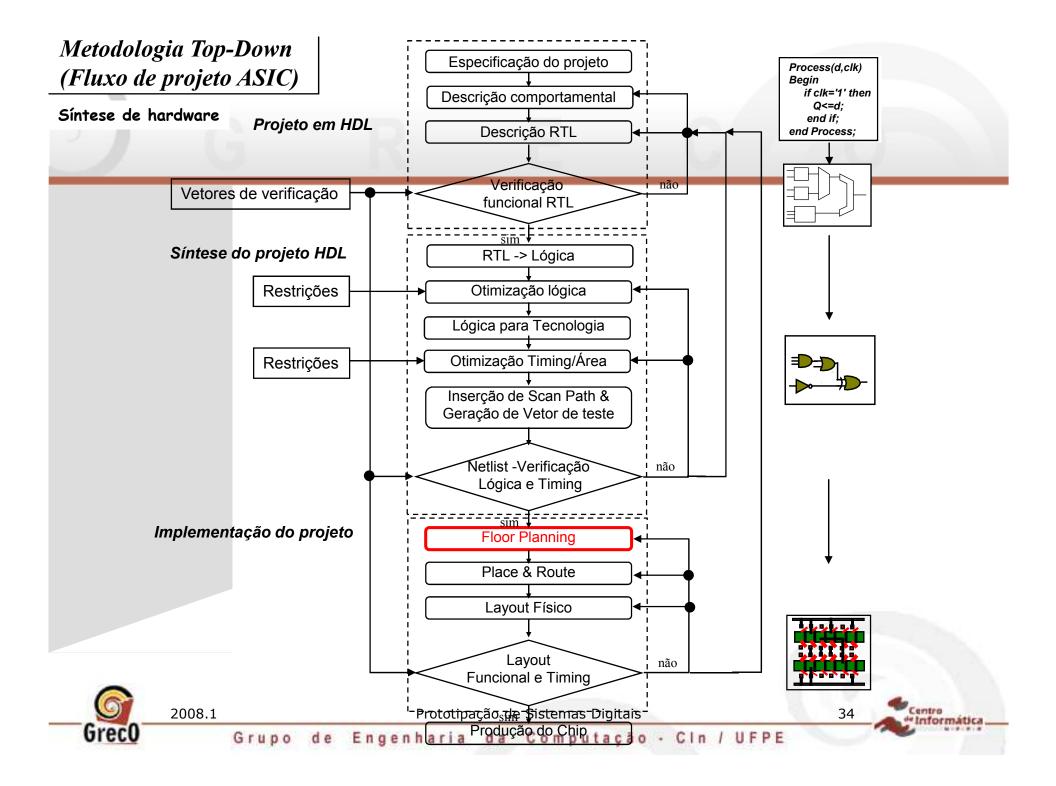

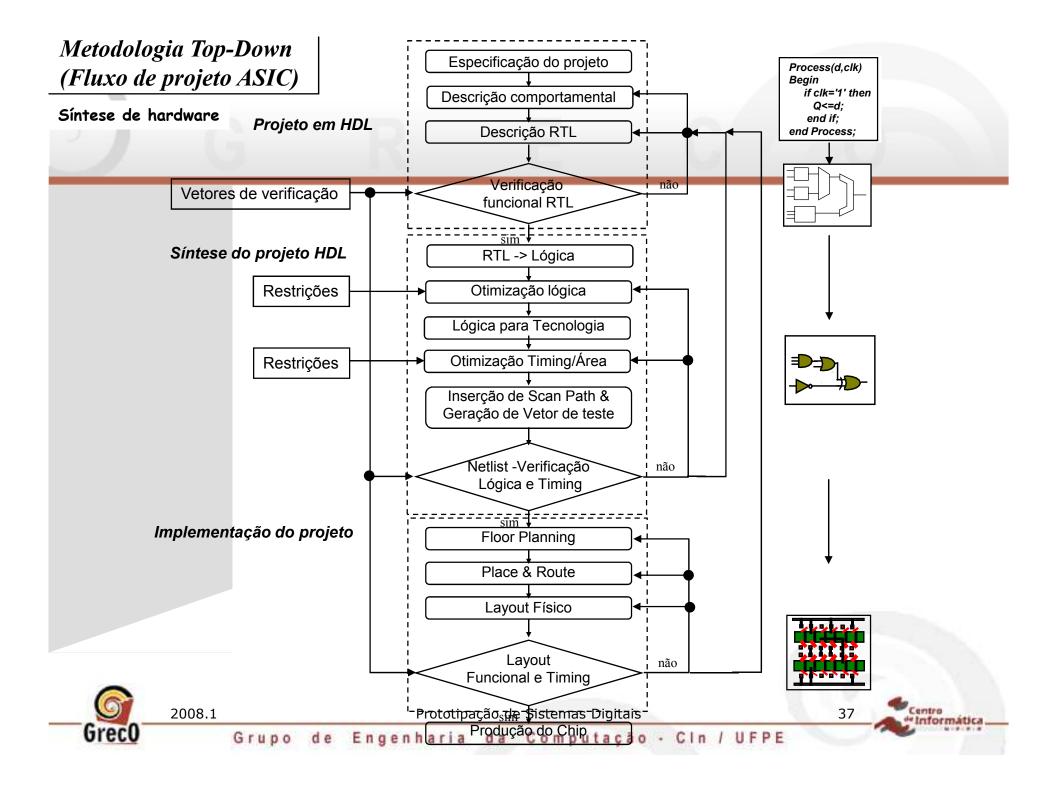

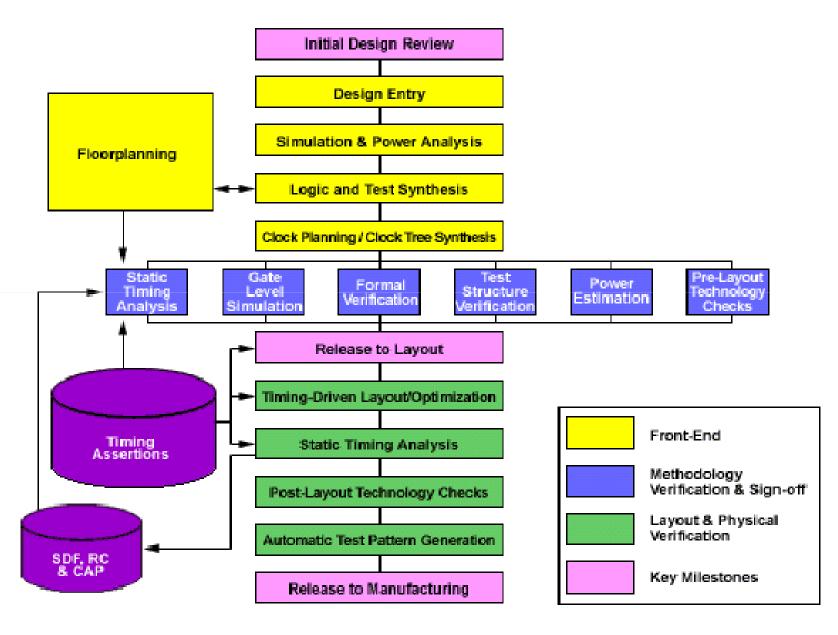

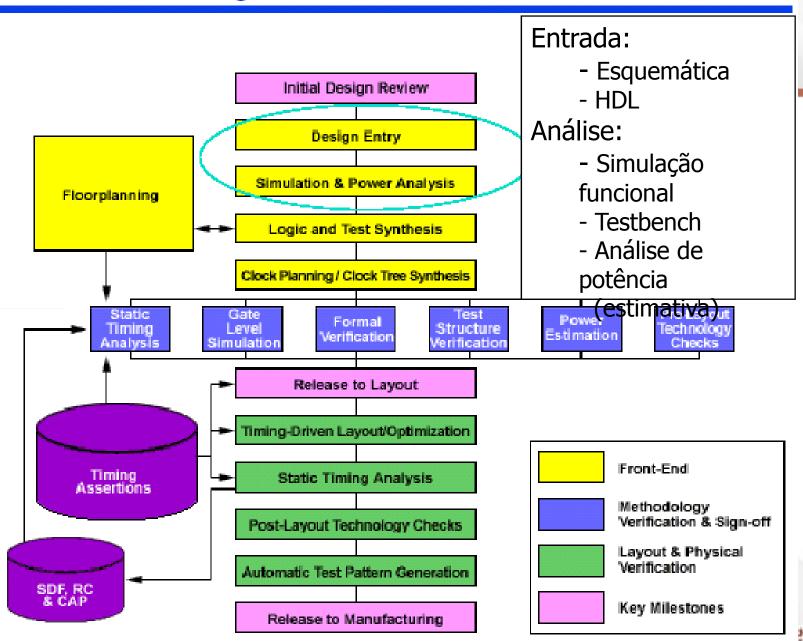

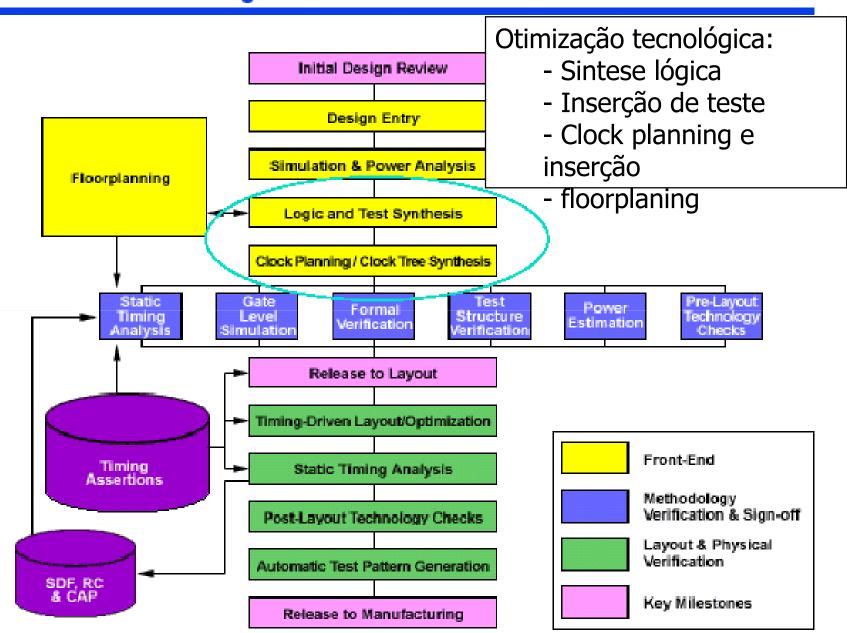

# Síntese de hardware Fluxo de projeto de ASICs

- ☐ Entrada da especificação

- Análise

- ☐ Otimização tecnológica

- ☐ Verificação de projeto

- ☐ Layout

## Níveis do projeto

#### **HDL View**

```

process(CLK)

begin

if (CLK = '1') and (not CLK'stable) then

s_counter_output <= s_counter_input and not s_reset;

s_ref_ctr_out <= s_load;

end if;

end process;</pre>

```

Independente da tecnologia

#### **Netlist View**

```

begin

U68: INVERT_A port map (Z => s_load, A => n265);

U87 : NOR3_4 port map (Z => n275, A => COUNTb(3),

B => COUNTb(4), C => COUNTb(0));

U88 : NOR3_4 port map (Z => n275, A => COUNTb(3),

B => COUNTb(4), C => COUNTb(0));

s_ref_ctr_out_reg : D_F_LPH0001_4 port map (L2 => s_ref_ctr_out, D => s_load, E => CLKb);

end SYN_refctr_rtl;

```

Dependente da tecnologia

#### Physical View

Dependente da tecnologia

Centro Informática....

### Exemplo - projeto

# Entrada VHDL (contador)

(independente da tecnologia)

```

entity refetr is

port (COUNT: in std ulogic vector(5 downto 0);

CLK: in std ulogic;

RESET: out std ulogic);

architecture refetr rtl of refetr is

signal s ref ctr out : std ulogic;

signal s load

: std ulogic;

: std ulogic vector(5 downto 0);

s next ctr val

s counter input

: std ulogic vector(5 downto 0);

s counter output

: std ulogic vector(5 downto 0);

: std ulogic vector(5 downto 0);

s reset

begin

s reset(0) <= RESET;

process (CLK)

begin

if (CLK = '1') and (not CLK'stable) then

s counter output <= s counter input and not s reset;

s ref ctr out <= s load;

end if:

end process;

end refetr rtl;

IBM

```

2008.1

# Simulação - funcional

2008.1

Prototipação de Sistemas Digitais

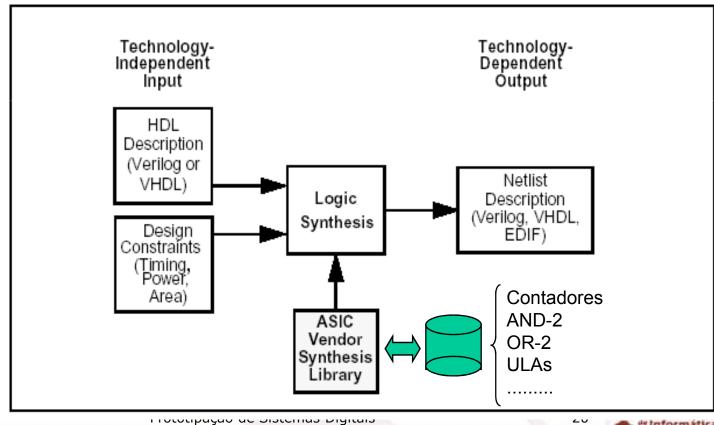

# Síntese Lógica

Síntese lógica tem como entrada uma descrição HDL-RTL, independente de tecnologia e, mapea o projeto em uma biblioteca de circuitos lógicos (células) fornecidos pelo fabricante.

2008.1

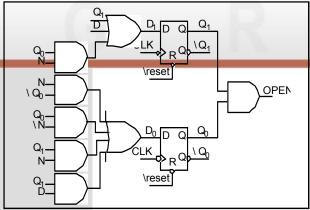

# Síntese Lógica - Possíveis saídas

□ Como saída, a síntese lógica gera uma netlist que pode ser escrita em diferentes linguagens.

```

netlist

schematic view

entity bombom01 is

port( reset, clk, c, d : in bit;

netlist

architecture arc bombons of bombom01

in VHDL

Síntese Lógica

is

begin

process (clk)

netlist

begin

if (reset = '1') then

in Verilog

estado atual <= tem zero;

libera bombom <= '0';

elsif (clk = '1' and clk'event) then

netlist

in EDIF

2008.1

```

Grupo de Engenharia da Computação - Cin / UFPE

mática

**IBM**

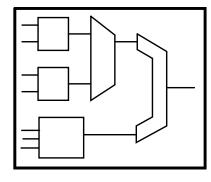

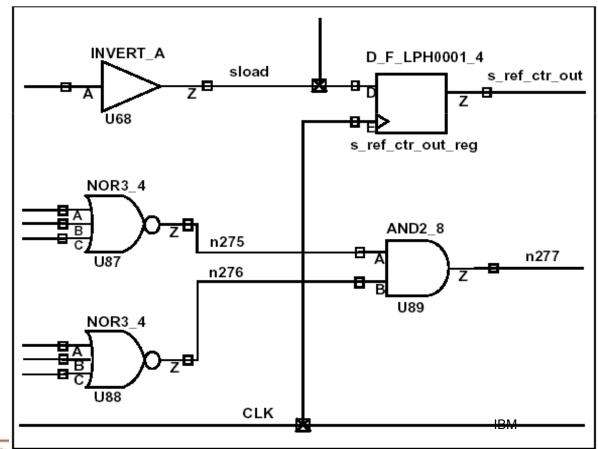

# Visão- Esquemática

☐ Os circuitos podem ser representados graficamente por um esquema baseado

nas células básicas da biblioteca do fabricante.

2008.1

PER PER PER

## Visão - Geração da Netlist

#### VHDL

```

entity refetr is

architecture SYN refetr rtl of refetr is

component INVERT A

port(E : out std logic; A : in std logic);

end component;

component NOR3 4

port (Z : out std logic; A, B, C : in std logic);

end component;

component AND2 8

port(Z : out std logic; A, B : in std logic);

end component;

component D F LPH0001 4

port(L2 : out std logic; D, E : in std logic);

end component;

begin

U68 : INVERT A port map (Z => s load, A => n265);

U87 : NOR3 4 port map (Z => n275, A => COUNT(3),

B \Rightarrow COUNT(4), C \Rightarrow COUNT(0));

U88 : NOR3 4 port map (Z => n276, A => COUNTb(5),

B \Rightarrow COUNT(2), C \Rightarrow COUNT(1));

s ref ctr out reg : D F LPH0001 4 port map (L2 =>

s ref ctr out, D => s load, E => CLK);

end SYN refetr rtl;

```

#### Verilog

```

module refetr (COUNT, CLK, RESET, REF);

INVERT A U68 (.Z(s load), .A(n265) );

NOR_4 U87 (.Z(n275), .A(COUNT[3]),

.B(COUNT[4]), .C(COUNT[0]));

NOR3 4 U88 (.Z(n276), .A(COUNT[5]),

.B(COUNT[2]),.C(COUNT[1]) );

AND2 8 U89 (.Z(n277),.A(n275),

.B(n276));

D F LPH0001 4 s ref ctr out reg(

.L2(s ref ctr out), .D(s load), .E(CLK));

endmodule;

```

2008.1

Gru

**IBM**

#### Visão - Netlist EDIF

#### **EDIF**

```

(cell refctr (cellType GENERIC)

(contents

(instance U68

(viewRef Netlist representation

(cellRef INVERT A(libraryRef IBMCMOS5S SC))

(instance U87

(wiewRef Netlist representation

(cellRef NOR3 4(libraryRef IBMCNOS5S SC))

(instance USS

(viewRef Netlist representation

(cellRef NOR3 4(libraryRef IBMCNOS5S SC))

(instance U89

(viewRef Netlist representation

(cellRef AND2 8 (libraryRef IBMCMOS5S SC))

(instance s ref ctr out reg

(viewRef Netlist representation

(cellRef D F LPH0001 4

(libraryRef IBMCMOS5S SC))

```

#### EDIF (continued)

```

(net s load

(joined (portRef A (instanceRef U74))

(portRef D (instanceRef s ref ctr out reg))

(portRef Z (instanceRef U68))

(net CLK

(joined (portRef CLK) (portRef E (instanceRef

(s ref ctr out reg))

(portRef E (instanceRef s counter output .....

net s ref ctr out

(joined (portRef D0 (instanceRef U90))

(portRef L2 (instanceRef s ref ctr out reg))

(net 275

(joined (portRef A (instanceRef U89)) (portRef Z

(instanceRef U87)))

(net 276

(joined (portRef B (instanceRef U89)) (portRef Z

(instanceRef U88)))

(net 277

(joined (portRef SD instanceRef u90)) (portRef Z

(instanceRef U89)))

)))))

```

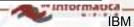

# Inserção de teste

#### ■ DFT - Design-For-Test

- Inserir estruturas, depois da síntese lógica, para permitir completo teste de manufatura do dispositivo.

- Flip-Flops normais são substituídos por elementos especiais que podem ser varridos (scannable)

200

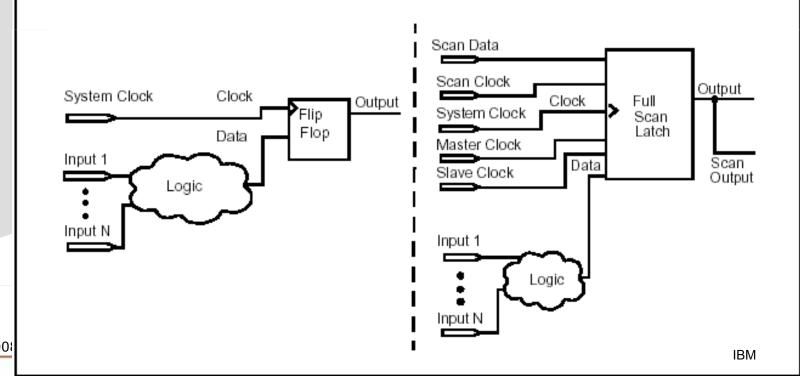

# Planejamento de relógio interno

|                                                    | A última fase da otimização tecnológica é a inserção da rede de                                       |

|----------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| relć                                               | ógio                                                                                                  |

| İI                                                 | nterno:                                                                                               |

|                                                    | Todo ASIC possui pelo menos um relógio(clock); circuitos complexos podem possuir mais que um relógio. |

| Parâmetros a serem considerados na rede interna de |                                                                                                       |

| relógio:                                           |                                                                                                       |

|                                                    | ☐ Área de silício;                                                                                    |

|                                                    | Atraso através da rede de relógio (clock) para circuitos que usam<br>relógio (latency);               |

|                                                    | ☐ A variação no tempo de chegada do relógio em vários elementos                                       |

|                                                    | que usam o relógio ( <b>skew</b> );                                                                   |

|                                                    | A potência gerada pela rede de relógio como switches.                                                 |

## Planejamento de relógio interno

- ☐ Empresas como a IBM usam árvore para relógio (clock tree) para propagar um sinal de relógio a centenas e milhares de circuitos lógicos que recebem um sinal de relógio.

- □ Antes da inserção da ávore, um projeto é dito ter relógios ideais, significando que todos os circuitos lógicos estão recebendo um dado sinal de clock em paralelo de um simples driver.

2008.1

Grupo de Engenha

# Verificação de projeto

- Nesta fase o projetista tem a oportunidade de verificar se as restrições de projeto estão sendo satisfeitas após a síntese do circuito:

- Funcionalidade do projeto está correta;

- Restrições físicas preliminares em termos de performance, testabilidade potência, tamanho, características elétricas.

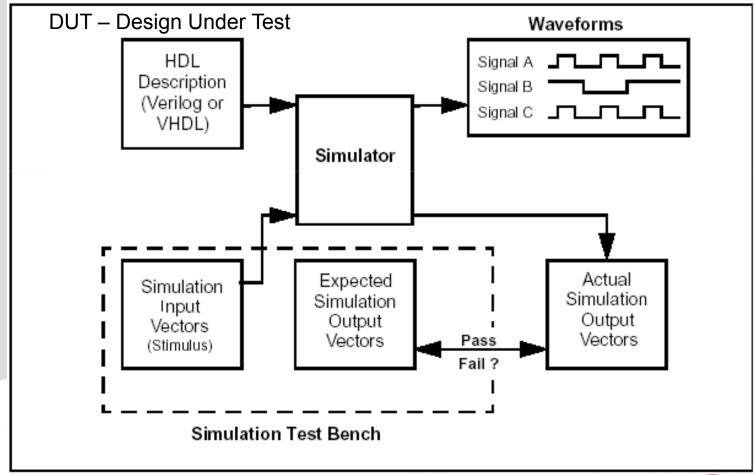

- ☐ Os circuitos podem ser verificados em vários níveis:

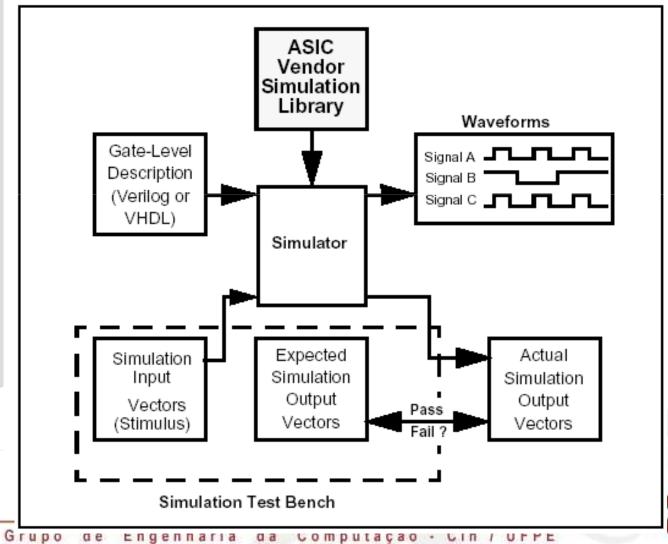

- Verificação funcional

- □ Verifica-se apenas a funcionalidade do circuito antes da síntese usando-se simulação. Em geral são gerados vetores de testes (estímulos), os quais são aplicados como vetores de entrada ao circuito em teste. Método não muito eficiente para circuitos de médio porte (100000 gates), devido ao tempo excessivo para se verificar grandes circuitos.

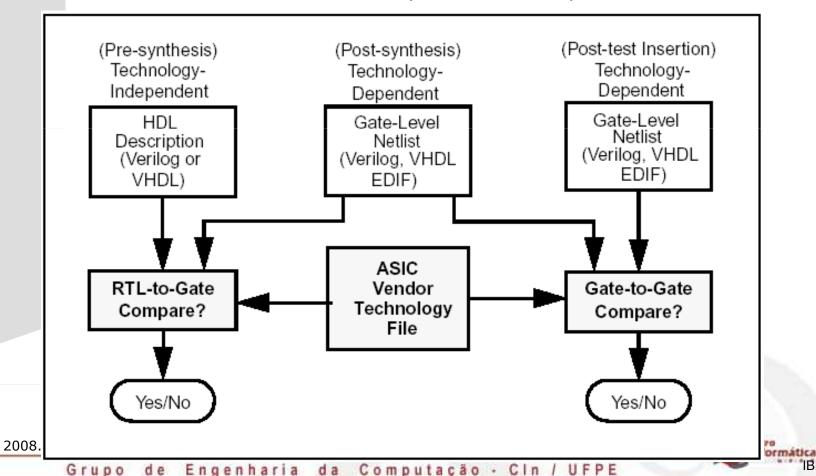

- Verificação formal

- Através de um modelo equivalente, é possível se chegar ao mesmo resultado de uma simulação. Neste caso, o circuito é quebrado em expressões lógicas Booleanas equivalentes e matematicamente avaliado através de comparações exaustivas. Neste método não há a necessidade de vetores de entrada ou saída. Indicado para circuitos com um grande número de gates.

2008.1

# Verificação Funcional Simulação - Nível de gate (Netlist)

2008.1

Centro de Informática. IBM

# Verificação Formal

☐ Este tipo de verificação tem o mesmo propósito da simulação a nível de gates, o qual é assegurar que a funcionalidade do projeto não tenha sido modificada ou corrompida durante o processo de síntese.

IBM

# Verificação de projeto

#### □ Verificação temporal

□ O objetivo desta fase é determinar se o projeto, uma vez mapeado em una tecnologia específica, atende os requisitos temporais previamente estabelecidos pelo usuário.

#### □ Potência

☐ Verificar a dissipação de potência de operação real do circuito nas condições normais de funcionamento.

#### ☐ Verificação Pré-layout

☐ Fase utilizada para se verificar, antes da geração final do layout do ciruito, aspectos relativos a conexão interna e externa de pinos (se estão todos adequadamente ligados), pinos especiais para teste, etc.

## Verificação de projeto

- Verificação da testabilidade (pós manufatura)

- Esta fase permite que o projetista detecte possíveis falhas de fabricação do chip, mediante o uso de uma série de testes funcionais similares a simulação a nível de gates. Padrões são aplicados aos testadores de circuitos (manufacturing testers). Estes testadores analisam características elétricas do silício verificando se determinada parte do circuito funciona adequadamente ou não.

- 1. Aqueles componentes que produziram os valores adequados (esperados) são ditos que passaram nos testes e portanto são componentes bons;

- 2. aqueles que não passaram nos teste são ditos que falharam.

- Exemplo (IBM):

- utiliza full-scan design-for-test (DTF).

- Fornece ao cliente um conjunto de ferramentas para geração de testbench.

Prototipação de Sistemas Digitais 33

2008.1

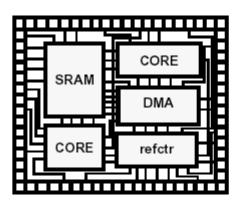

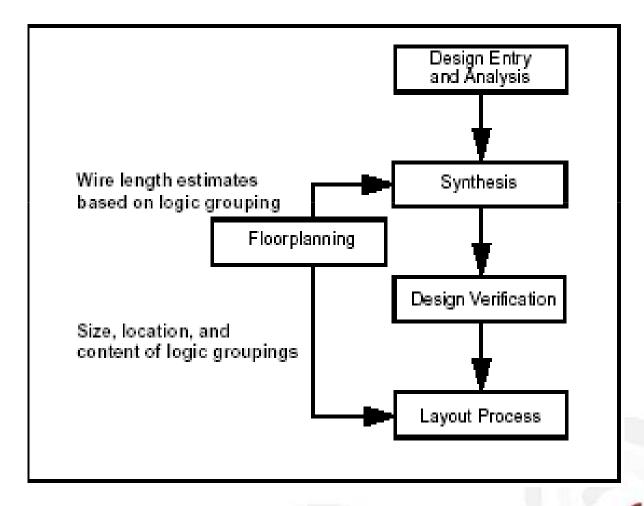

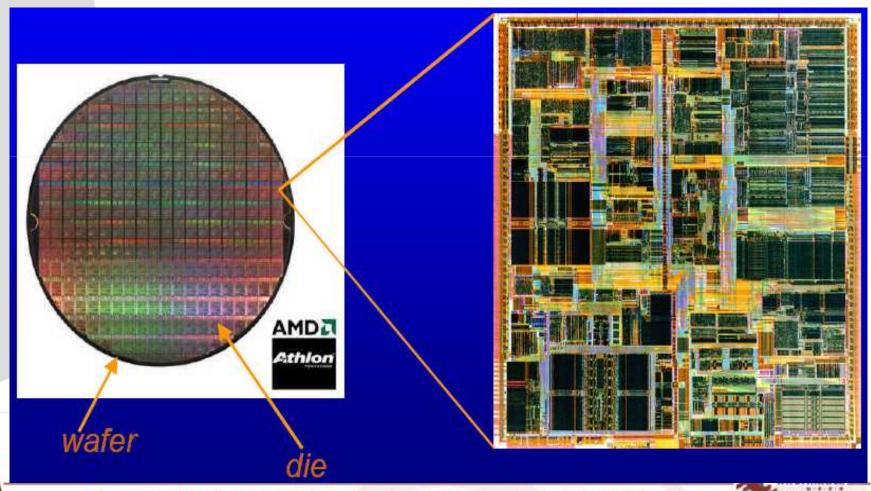

## Floorplanning

- ☐ Está é a fase na qual os blocos lógicos são colocados adequadamente dentro do espaço (loosing placement) de sílicio reservado para a implementação do circuito (die) observando performance e rotabiliadadae. Nesta fase devese levar em conta parâmetros como:

- Área

- Tamanho das redes

- Localização de pinos

- -

- O floorplanning permite ao projetista otimizar:

- a síntese lógica (escolha de melhores células), em função da velocidade, tamanho, etc.;

- ter uma visão geral da malha de redes do circuito;

- e gerar um modelo inicial otimizado para o processo de layout final do circuito.

# Floorplanning

Centro de Informática

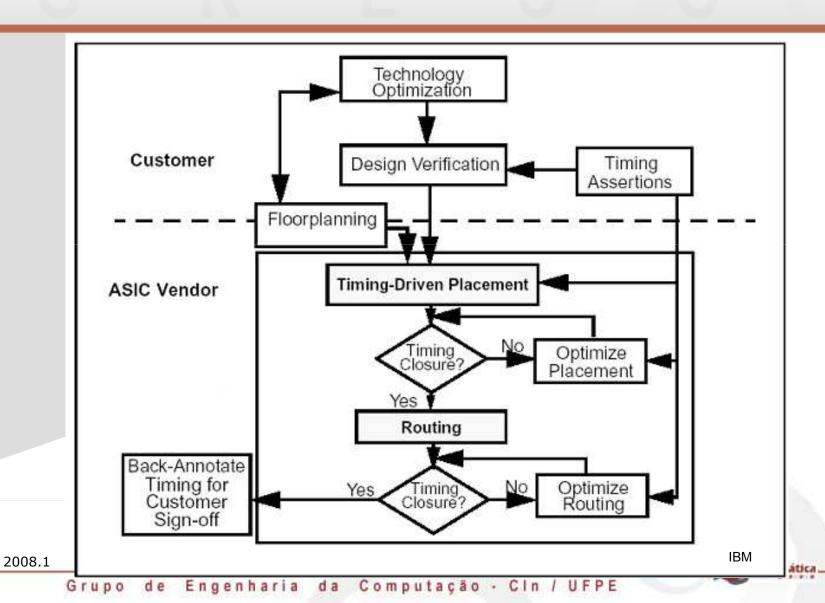

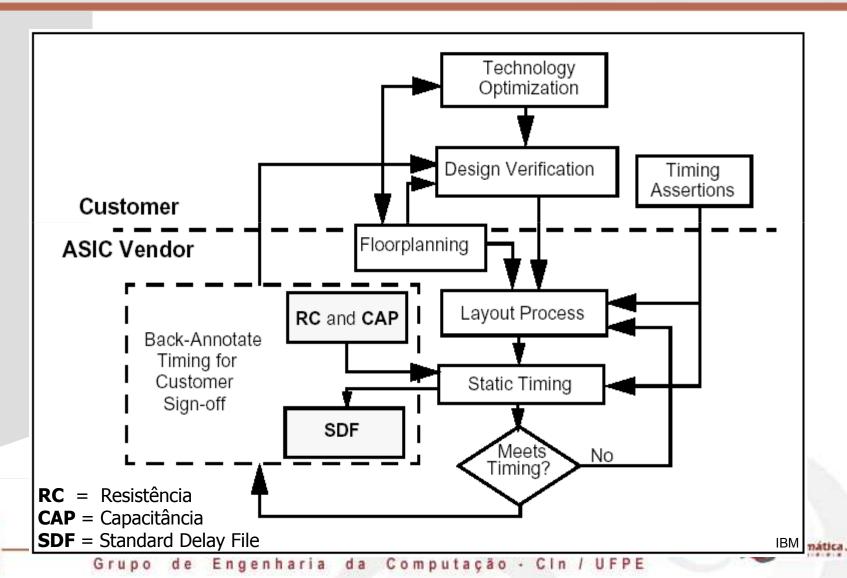

## Geração do layout (IBM)

Grec0

### Layout - Back - Annotation

# Fluxo de projeto Emulação/Implementação do componente de harwdare

Mesma base de dados para emulação e implementação

200 Testes durante a pamulação seriamimais próximos possíveis da implementação final do projeto "tação" con luppe

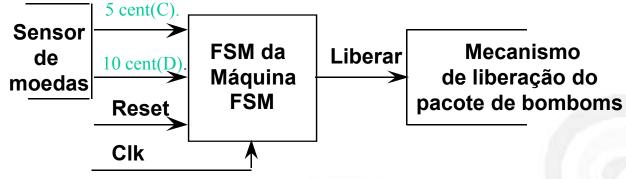

# Exemplo: Máquina de vender Bomboms

#### □ Descrição

- A máquina libera um pacote de bomboms se o cliente depositar pelo menos 15 centavos. A máquina não dá trôco.

- Moedas aceitas na máquina

- 5 centavos (C)

- 10 centavos (D)

- ☐ Diagrama da máquina

#### Diagrama de bloco

Centro

```

entity bombons is

port (

reset : in bit;

clk : in bit;

: in bit;

: in bit;

open : out bit

);

end bombons;

```

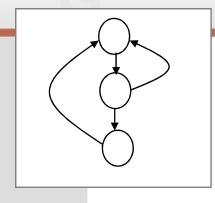

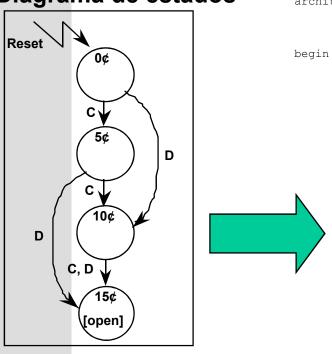

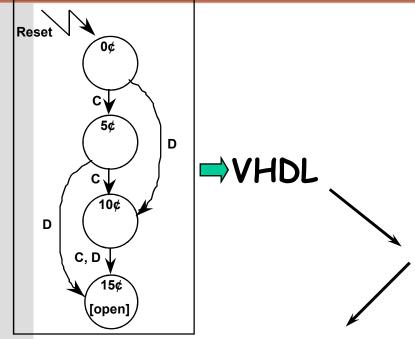

#### Diagrama de estados

Máquina de vender bombom (código VHDL)

```

architecture arc bombons of bombons is

type estados is (tem zero, tem cinco, tem dez, tem quinze);

signal estado atual : estados;

process (reset, clk)

begin

if (reset = '1') then

estado atual <= tem zero;

open <= '0';

elsif (clk = '1' and clk'event) then

case estado atual is

when \overline{\text{tem}} zero =>

if (c = '1') then

estado atual <= tem cinco;

elsif (d = '1') then

estado atual <= tem dez;</pre>

end if;

when tem cinco =>

if (c = '1') then

estado atual <= tem dez;

elsif (d = '1') then

estado atual <= tem quinze;

open <= '1';

end if;

when tem dez =>

if (c = '1') then

estado atual <= tem quinze;

open <= '1';

elsif (d = '1') then

estado atual <= tem quinze;

open <= '1';

end if;

when tem quinze =>

estado atual <= tem zero;

open <= '0';

```

2008.1

Prototipação de Sistemas Digitais

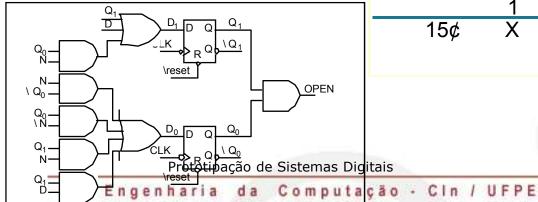

# Síntese

#### Diagrama de estados

#### Diagrama esquemático da FSM

#### Tabela de estados

| Present<br>State | INI<br>D         | PUT<br>C         | Next<br>State          | Output<br>Open        |

|------------------|------------------|------------------|------------------------|-----------------------|

| 0¢               | 0<br>0<br>1<br>1 | 1010             | 0¢<br>5¢<br>10¢<br>X   | 0<br>0<br>0<br>X      |

| 5¢               | 0<br>0<br>1<br>1 | 0<br>1<br>0<br>1 | 5¢<br>10¢<br>15¢<br>X  | 0<br>0<br>0<br>0<br>X |

| 10¢              | 0<br>0<br>1<br>1 | 0<br>1<br>0<br>1 | 10¢<br>15¢<br>15¢<br>X | 0<br>0<br>0<br>0<br>X |

| 15¢              | X                | X                | 15¢                    | 1                     |

2008.1

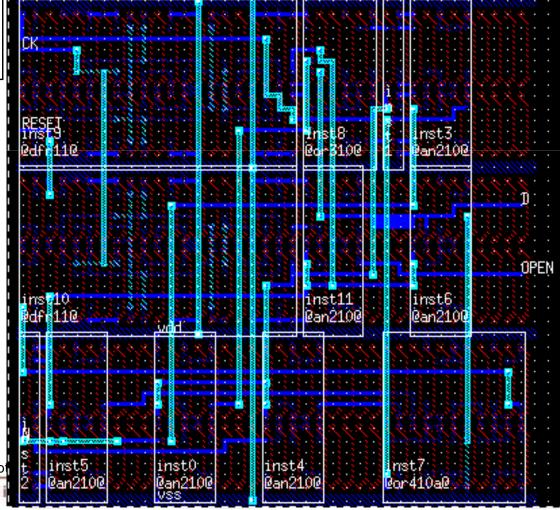

#### Diagrama esquemático da FSM

#### Layout

- Placement

- Detailed Routing

2008.1

Proto

Grupo de Engenhar

## Exemplo 2 - layout

#### The IBM ASIC Design Flow

CSE477 L26 Trend 3 Irwin&Vijay&Xie, PSU, 2004

#### The IBM ASIC Design Flow

#### Entrada e análise

IBM

#### The IBM ASIC Design Flow Otimização tecnológica

CSE477 L26 Trend 9 Irwin&Vijay&Xie, PSU, 2004