## Máquinas de Estados Finitos

Aula 19

Prof. Abel Guilhermino

## Definição

- Um sistema seqüencial deve ter a capacidade de capturar a influência de todas as entradas passadas sobre as saídas atuais e futuras.

- Os valores das seqüências de entrada podem ser agrupados em um número finito de classes de tal maneira que todas as funções no tempo que têm o mesmo efeito sobre a saída no tempo t ≥ t₁ são incluídas na mesma classe.

- Como resultado, a determinação de z(t) não precisa da seqüência de entrada inteira x(0,t) porque basta saber a classe à qual a função pertence.

- A classe é mantida em uma variável auxiliar s chamada estado, a qual também é uma função do tempo.

- Uma vez que o número de classes (isto é, o número de estados do sistema) é finito, os sistemas são chamados de sistemas de estados finitos ou máquinas de estados finitos.

## Representação FSM

- O estado de um sistema seqüencial usa três variáveis no tempo:

- A entrada

- O estado

- A saída

- Além disso há duas funções:

- Função transição de estado

- Ou apenas funções de transição, a qual produz o próximo estado, como uma função da entrada atual x(t) e do estado atual s(t).

- Função de saída

- A qual produz a saída atual z(t) como uma função da entrada atual e do estado atual.

## Representação FSM

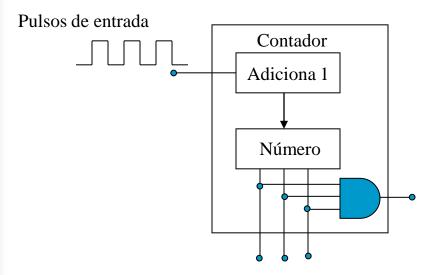

Para melhor explicar representação máquinas de estados finitos, partimos de um exemplo de uma lógica seqüencial de um

contador.

- A unidade é projetada para contar pulsos à medida que eles chegam na entrada X.

- número de pulsos indicado na palavra binária de 3 bits  $n_2 n_1 n_0$ .

- Palavra limitada à faixa 0-7.

- Saída R definida por:

- R=0 (contador na faixa 0-6)

- R=1 (contador em 7)

## Representação FSM

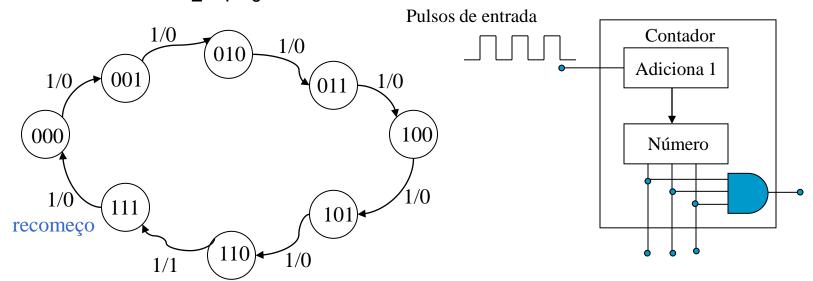

- Essas definições caracterizam o ciclo do valor de n<sub>2</sub>n<sub>1</sub>n<sub>0</sub> de acordo com a seqüência:

- $\bullet$  000 $\to$ 001 $\to$ 010 $\to$ 011 $\to$ 100 $\to$ 101 $\to$ 110 $\to$ 111 $\to$ 000..

- Terminologia:

- ◆ Definimos cada possível valor da palavra n₂n₁n₀

como sendo um estado distinto da máquina.

- Isto significa que existem 8 possíveis estados nos quais o circuito pode estar.

- Para descrever a operação do circuito, utilizamos desenhos chamados diagrama de estados.

### Diagrama de estados

- É uma forma de representação através de desenhos usados para descrever a operação de um circuito.

- Os diagramas de estados mostram todos os estados individuais da máquina e as possíveis seqüências de mudança do circuito de um estado para o outro.

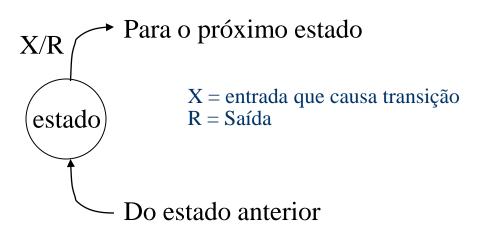

- O elemento básico consiste de um círculo que mostra o estado, com setas entrando/saindo para mostrar as transições para e do estado, respectivamente.

## Diagrama de estados

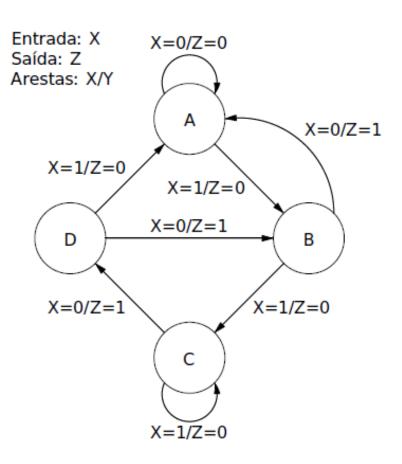

- Na notação do desenho, utilizamos X/R para denotar o valor da entrada X responsável pela transição na direção mostrada e o valor da saída R quando a transição ocorre.

- Cada círculo deve ter linhas que mostram o que acontece para cada possível valor de X.

## Diagrama de estados

- Diagrama de estados para o contador

- Como a seqüência é bem-definida, um pulso de entrada de X=1 causa uma transição para o próximo estado.

- ◆ A saída R é 0, a menos que o contador atinja o valor de n₂n₁n₀=111, resultando em R=1.

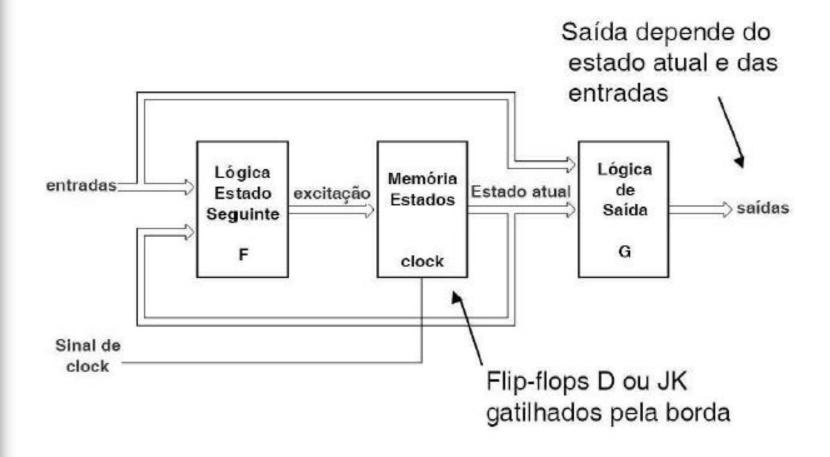

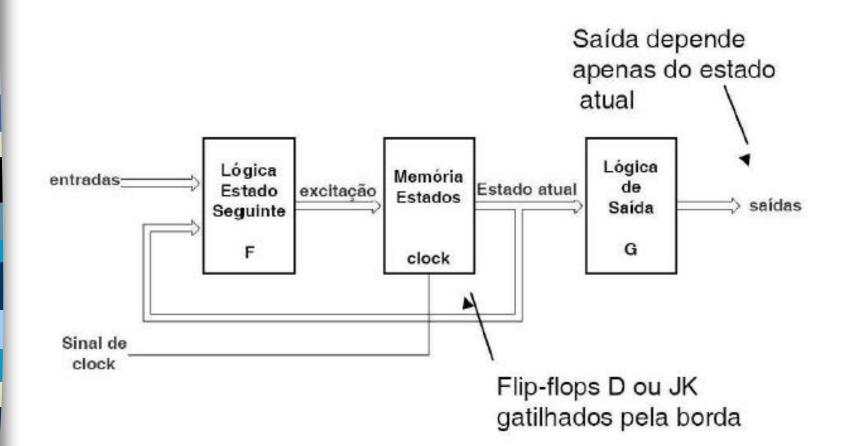

## Máquinas de Estados

- É um circuito sequencial que transita numa sequência pré-definida de estados

- A transição entre estados é comandada por uma sinal de controle.

- O estado atual é definido por um elemento de memória, e o estado futuro é determinado com base no estado atual e na condição das entradas.

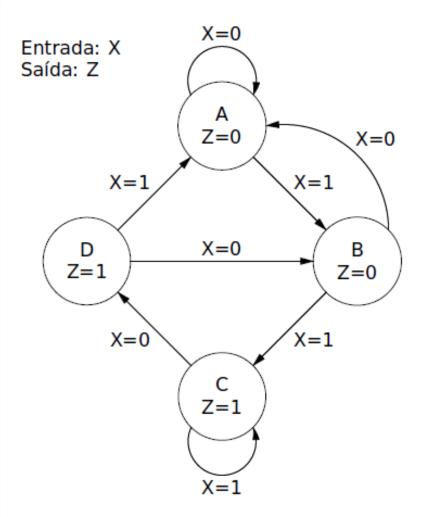

## Máquina de Estados de Mealy

## Máquina de Estados de Moore

## Máquina de Moore x Mealy

#### Moore

- Saídas dependem apenas do estado atual

- As saídas apenas são escritas quando os estados variam (transições de estados são síncronos)

#### Mealy

- As saídas dependem de ambos:entradas e estados

- Quando a entrada muda, as saídas são atualizadas imediatamente, sem esperar por clock

## Circuito Síncrono (Clock único)

- Receita para circuitos sequenciais robustos:

- As saídas dos circuitos combinacionais são analisadas apenas durante a subida de clock

- O período de clock deve ser maior do que qualquer atraso combinacional

- Os estados devem mudar apenas depois que todas as transições lógicas forem finalizadas

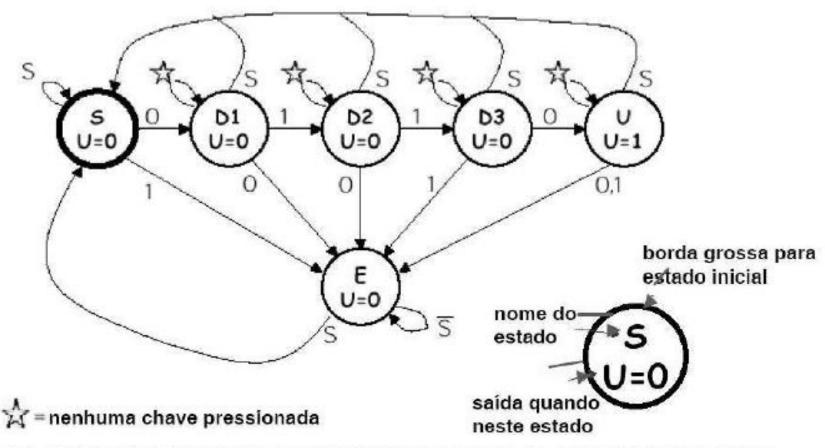

## Lógica Sequencial

- A lógica sequencial é usada quando precisamos organizar a solução através de uma sequência de passos:

- Exemplo: Como abrir uma fechadura com uma combinação digital. A fechadura possui três botões

- "start", "O", "1".

- Passo 1: pressione o botão "Start"

- Passo 2: pressiono o botão "O"

- Passo 3: pressiono o botão "1"

- Passo 4: pressiono o botão "1"

- Passo 5: pressiono o botão "O"

## Implementação Máquina de Moore

Diagrama de Estado

obs. verificar que sempre que a chave START é pressionada, a seqüência volta para o estado jnicial S.

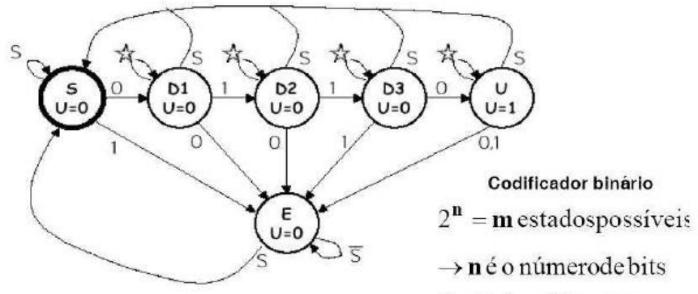

## Diagrama de estados Máquina de Moore

6 estados diferentes : codificados por 3 bits

Arcos saindo de um estado devem ser:

- (1) mutuamente exclusivos

não pode ter duas opções para um mesmo valor de entrada

- (2) coletivamente exaustivo todo estado deve especificar o que acontece para cada entrada possível. "Nada acontece" significa que o arco deve voltar para o mesmo estado.

## Tabela de Transição de Saída Máquina de Moore

| Estado atual Q <sub>0</sub> Q <sub>1</sub> Q <sub>2</sub> |     | <b>B</b> 'start" | <b>B</b> 1" | <b>B</b> "0" | Estado seguinte<br>(Q <sub>0</sub> Q <sub>1</sub> Q <sub>2</sub> )* | saída U<br>unlock |

|-----------------------------------------------------------|-----|------------------|-------------|--------------|---------------------------------------------------------------------|-------------------|

|                                                           |     | 1                | ***         | ***          | start 000                                                           | 0                 |

| Sstart                                                    | 000 | O                | 0           | 1            | digit1 001                                                          | 0                 |

| Sstart                                                    | 000 | 0                | 1           | O            | error 101                                                           | 0                 |

| S start                                                   | 000 | O                | 0           | 0            | start 000                                                           | O                 |

| D1digit1                                                  | 001 | 0                | 1           | 0            | digit2 O10                                                          | 0                 |

| D1digit1                                                  | OO1 | O                | 0           | 1            | error 101                                                           | 0                 |

| D1 <sub>digit1</sub>                                      |     | 0                | 0           | 0            | digit1 001                                                          | 0                 |

| D2digit2                                                  |     | 0                | 1           | 0            | digit3 O11                                                          | 0                 |

| D2digit2                                                  |     | 0                | 0           | 1            | error 101                                                           | O                 |

| D2digit2                                                  |     | 0                | 0           | 0            | digit2 010                                                          | 0                 |

| D3 digit3                                                 | 011 | O                | 0           | 1            | unlock 100                                                          | 0                 |

| D3digit3                                                  | 011 | 0                | 1           | O            | error 101                                                           | 0                 |

| D3digit3                                                  | 011 | 0                | O           | 0            | digit3 O11                                                          | O                 |

| Uunlock                                                   | 100 | 0                | 1           | 0            | error 101                                                           | 1                 |

| U unlock                                                  | 100 | O                | O           | 1            | error 101                                                           | 1                 |

| U unlock                                                  | 100 | 0                | 0           | O            | unlock 100                                                          | 1                 |

| E error                                                   | 101 | 0                |             |              | error 101                                                           | O                 |

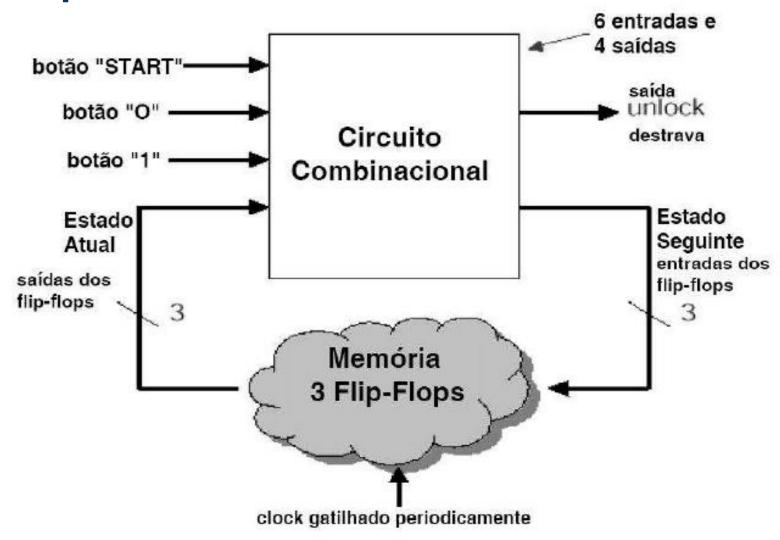

## Implementação do Hardware Máquina de Moore

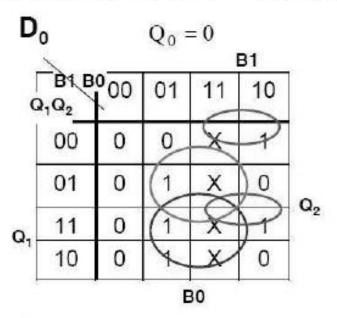

## Mapas de Karnaugh

- Quando o botão "START" for 1, o circuito irá permanecer ou voltar para o estado inicial '000'. Portanto, podemos ligar o botão "START" no botão "RESET" dos flip-flops.

- Usando flip-flop tipo D equação característica → (Q<sub>0</sub> Q<sub>1</sub> Q<sub>2</sub>)\* = (D<sub>0</sub> D<sub>1</sub> D<sub>2</sub>)

$$Q_0^* = D_0 = \underbrace{Bl(\overline{Q_1Q_2} + Q_1Q_2) + B0(Q_2 + Q_1) + Q_0}_{\text{Equação de excitação ou transição}}$$

saída U = unlock =

$$Q_0 \overline{Q_2}$$

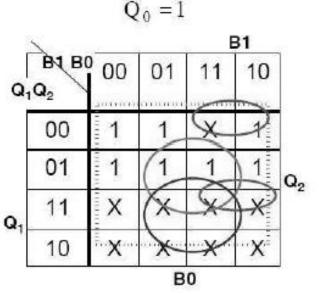

## Diagrama de estado – Exemplo (Máquina Mealy)

- Exemplo:

- Projete um circuito que gere saída '1' quando for observado 3 uns '1's consecutivos na entrada. Nos demais casos a saída deve ser zero ('0').

# Máquina de Estado Finito Síncrono (Verilog)

```

module mef (clk, in_data, out_data);

input clk;

input [N:0] in_data; output [M:0] out_data;

reg [M:0] out_data;

reg [S:0] estado;

always @(negedge clk)

case (estado)

0 : begin output <= .....; estado <= .....; end

1 : begin output <= .....; estado <= .....; end

default : begin output <= .....; estado <= .....; end

endcase

endmodule

```

## Máquina de Moore

Sinal de reset:  $\rightarrow$  A.

```

module moore(clk, X, Z, rst);

input clk, X, rst;

output Z; reg Z;

parameter[1:0] A=2'b00, B=2'b01,

C=2'b10, D=2'b11:

reg [1:0] estado, prox_estado;

always @(posedge clk)

if (rst) estado <= A;

else estado <= prox_estado;

always @(estado or X) begin

Z = (estado == C \mid | estado == D);

case(estado)

A: if (X) prox_estado = B;

else

prox_estado = A;

B: if (X) prox_estado = C;

else

prox_estado = A;

C: if (X) prox_estado = C;

else

prox_estado = D;

D: if (X) prox_estado = A;

prox_estado = B;

else

endcase

end

endmodule

```

## Máquina de Mealy

```

module mealy(clk, X, Z, rst);

input clk, X, rst;

output Z; reg Z;

parameter[1:0] A=2'b00, ...

reg [1:0] estado, prox_estado;

always @(posedge clk)

if (rst) estado <= A;

else estado <= prox_estado;

always @(estado or X)

case(estado)

A: if (X) begin

prox_estado = B; Z=1'b0;

end

else begin

prox_estado = A; Z=1'b0;

end

B: if (X) begin

prox_estado = C; Z=1'b0;

end

else begin

prox_estado = A; Z=1'b1;

end

C: ... D: ...

endcase

endmodule

```